声音的产生是由于发声物体以一定的频率振动,带动周围的空气振动,使动耳朵内的听小骨一起振动,这些振动被转换为微弱的电子脑波,它就使我们觉察到了声音。不同的发声物体(声源)音色不同。声源振动的快慢不一样即产生的频率不一样,故有高音、低音、中高音、中低音等区分。由于声源振动的幅度大小不一样,所以我们听到的声音有大小的区分。本文主要通过对输入的时钟频率按不同的分频比进行分频,以达到产生不同频率的声音。

1 音频发生器基本原理及顶层设计

音频发生是基于声音的发生原理,利用外部晶振输入固定的频率(12MHz),由内部进行不同的分频得到,由于从数控分频器出来的信号是脉冲极窄的脉冲信号,为了能有效的驱动扬声器,需要外加一个D触发器以便于均衡占空比,这样出来的信号的频率就只有原信号的一半(6MHz)。

本音频发生器主要实现两个功能,通过按键选择。功能一可以通过按键让喇叭发出不同频率的声音,功能二可以预播放预设置的音频。

2 底层模块设计

图1 音频发生器顶层各模块连接图

2.1 按键模块

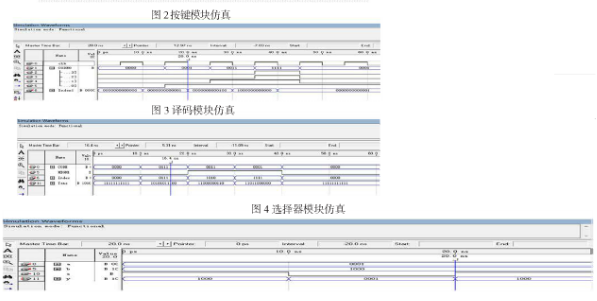

由于本模块可以实现13个不同的音调(7个低音,6个高音),所以在按键模块有13个拨码开关输入,采用编码的方式把13中不同的编码转换为4为的数据输出。为了同步于自动播放的模块,本模块与自动模块采用同一时钟信号(8Hz),以上升沿触发的形式触发得到按键的输入。

2.2 信号选择模块

由于本模块可以实现自动播放于手动输入音调的功能,为此为了能实现单一的信号输入,必须在音频信号处理之前对输入的信号给予选择。此模块有三个信号输入,一个信号选择短,两个输入信号。还有一个信号输出端,对于选中的信号直接输出。

2.3 自动信号产生模块

由于本模块可以实现自动播放内置歌曲的功能,所以必须要有一个模块来产生播放信号,此模块由8Hz 时钟输入,以计时器的方式产生4位的信号输出。

2.4 译码模块

此模块的输入由选择器的输出的得,由于选择的输出是4位数据,所以需要由此模块进行译码以判断输出的高音/ 低音,也便把输入的数据输出显示,并且的到分频比以便于用于下一模块的分频。

2.5 分频模块

此模块有输入12MHz时钟频率,由输入的4位总线型数据控制对12MHz的信号进行不同比例的分频,然后经D触发器进行脉冲展宽,使扬声器有足够的功率发音。

如:将PreCLK为CLK的16分频

DivideCLK : PROCESS(clk)

VARIABLE Count4 : STD_

LOGIC_VECTOR (3 DOWNTO 0) ;

BEGIN

PreCLK 11 THEN PreCLK

经过仿真,证实系统方案可行。