1 前言

LonWorks现场总线是美国Echelon公司推出的局部操作网络,它具有统一性、开放性、互操作性及支持多种通信介质等优良性能,是当今最流行的现场总线之一。但是由于LonWorks控制节点的核心神经元芯片(Neuron Chip)的应用处理能力相对较弱,因而对于复杂的应用常使用主从处理器结构,主处理器完成用户的应用功能,而把Neuron芯片作为通信协处理器。由于可以提高了节点的处理能力,节省资金和开发时间,因此,具有多功能的通用嵌入式主处理器具有很好的应用前景。本文采用的MSP430F149主处理器是TI公司基具有较高的集成度的芯片,简化了应用系统的硬件设计,适合作为多用途智能节点。

2 ShortStack的介绍和实现

2.1 ShortStack的结构

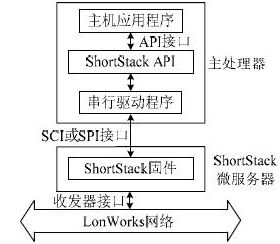

ShortStack微服务器是Echelon公司提供的一套开发包,其结构图如下:

图1 ShortStack结构图

由图可看到,主处理器与ShortStack 微服务器通信通过ShortStack API函数来实现,通常使用其中的5个,lonInit(),lonEventHandler(),lonPropagateNv(),lonPollNv()和lonsendServicePin()。ShortStack Micro Server,运行ShortStack固件,运行LonTalk协议的1~6层;主处理器运行SCI串口驱动程序,运行ShortStack API函数,处理与Lonworks其他节点通信;主处理器应用部分调用ShortStack API函数。主处理器设备的接口支持文件,由Neuron C model file 通过使用ShortStack向导来产生,产生数据表定义网络变量和收发器参数。而Model file只需要声明网络变量NVs,配置属性CPs和功能模块FBs,因此,可以不需要熟悉Neuron C。

串行驱动程序为主处理器和从处理器之间提供一个独立的接口。整个串行驱动程序由两部分构成:上层驱动程序为主应用程序提供一个接口;底层驱动程序完成与神经元芯片的硬件接口。上层和底层驱动之间的数据交换通过缓冲队列完成。底层驱动程序与从处理器的通讯包括SCI上传和SCI下传两类,SCI上传是数据由神经元芯片上传到主处理器;SCI下传是数据由主处理器下传到神经元芯片。

2.2 ShortStack的软件实现

采用提供的Neuron C模板事例修改编写。主要修改ldvsci.h和ldvsci.c中与MSP430F149处理器相关的语句。

在ldvsci.h中,修改为:

#define ENABLE_RX_TX() (ME1 | = UTXE0+URXE0)

#define ENABLE_TX_ISR() (IE1 |= 0x80)

#define ENABLE_TX_COMPLETE_ISR() (IFG1|=0x80) //USART0发送标志

#define ENABLE_RX_ISR() (IE1|= 0x40) //enable SCI receive interrupt

#define DISABLE_TX_ISR() (IE1 &= ~0x80)

#define DISABLE_TX_COMPLETE_ISR() (IFG1 &= ~0x80) // USART0发送标志复位

#define DISABLE_RX_ISR() (IE1 &= ~0x40)

#define CHECK_RTS() (P2OUT& 0x02) // check RTS

#define CHECK_CTS() (P2IN& 0x01) // check CTS

#define ASSERT_RTS() (P2OUT &= ~0x02) // assert RTS

#define DEASSERT_RTS() (P2OUT|= 0x01) // deassert RTS

#define DEASSERT_HRDY() (P2OUT |= 0x04) // deassert _HRDY

#define ASSERT_HRDY() (P2OUT &= ~0x04) // assert _HRDY

在ldvsci.h中,修改了void SysResetSCI(void) ,void SysInit(void),

void SysUpdateWDT(void), @interrupt void RxInt (void)以及@interrupt void TxInt (void)中与MSP430F149相关的程序。

其他文件做少许改变,其中platform.h定义了BIG_ENDIAN and LITTLE_ENDIAN的区别,对应于哈佛结构和冯.诺伊曼体系结构。由于MSP430F149核是冯.诺伊曼体系结构的,所以ShortStack需用LITTLE_ENDIAN(即高字节存在高位地址)。

2.3 ShortStack的硬件件实现

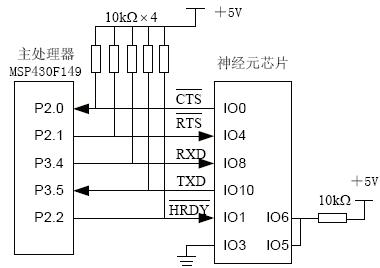

从处理器(如图2)采用TP/FT-10F控制模块,该模块由微型电路板构成, 包括一个3150 芯片、一块闪存、一个通信收发器、电源连接器、I/O 口和网络接口, 其中IO_0~IO_10 为神经元芯片3150 的11 个I/O 管脚用于对控制设备的连接, DataA 和DataB 是FTT- 10收发器与网络的连接口,它能够将主处理器经过处理输出的数据发送到LON 总线,也可以将LON 总线上的消息传送给主处理器。

主处理器与神经元芯片之间的通信采用SCI模式。SCI接口是一个半双工串行异步通信接口,通信的格式是:一个起始位,8个数据位和一个停止位(LSB在先)。通信模式的选择由IO3确定,IO3接地选择SCI通信模式。IO5、IO6则用来选择通讯速率。

3 μcos_Ⅱ的移植

μcos_Ⅱ的全部源代码,共16个文件。移植工作涉及的源文件分为三部分:与处理器无关的代码部分,这部分代码完成操作系统的基本功能,包括10个文件,即:OS_CORE.C,OS_MBOX.C,OS_MEM.C,OS_Q.C,OS_SEM .C,OS_TASK.C,OS_TIME.C.OS_FLAG.C,OS MUTEX.C,uCOS_II.H。设置代码部分,包括OS—CFG.H 和INCLUDES.H 两个头文件,用来进行操作系统配置。

图2 主从处理器连接图

最主要的部分是与处理器有关部分的代码,包括一个头文件OS_CPU.H、一个C代码文件OS_CPU_C.C 及一个汇编文件OS_CPU_A.ASM,将其移植到MSP430F149处理器上,需要修改这3个与体系结构相关的文件,代码量大约是500行。下面分别介绍这3个文件的移植。

OS_CPU.H这部分代码包括数据类型定义、堆栈单位定义、堆栈增长方向定义、关中断和开中断的宏定义以及进行任务切换的宏定义等。其中,为了在不同的工作模式下调用系统的底层接口函数不受访问权限的限制,使用软中断SWI。堆栈的单位与CPU的寄存器长度一致,结构常量OS_STK_GROWTH置1,表示堆栈从由高地址向低地址增长。