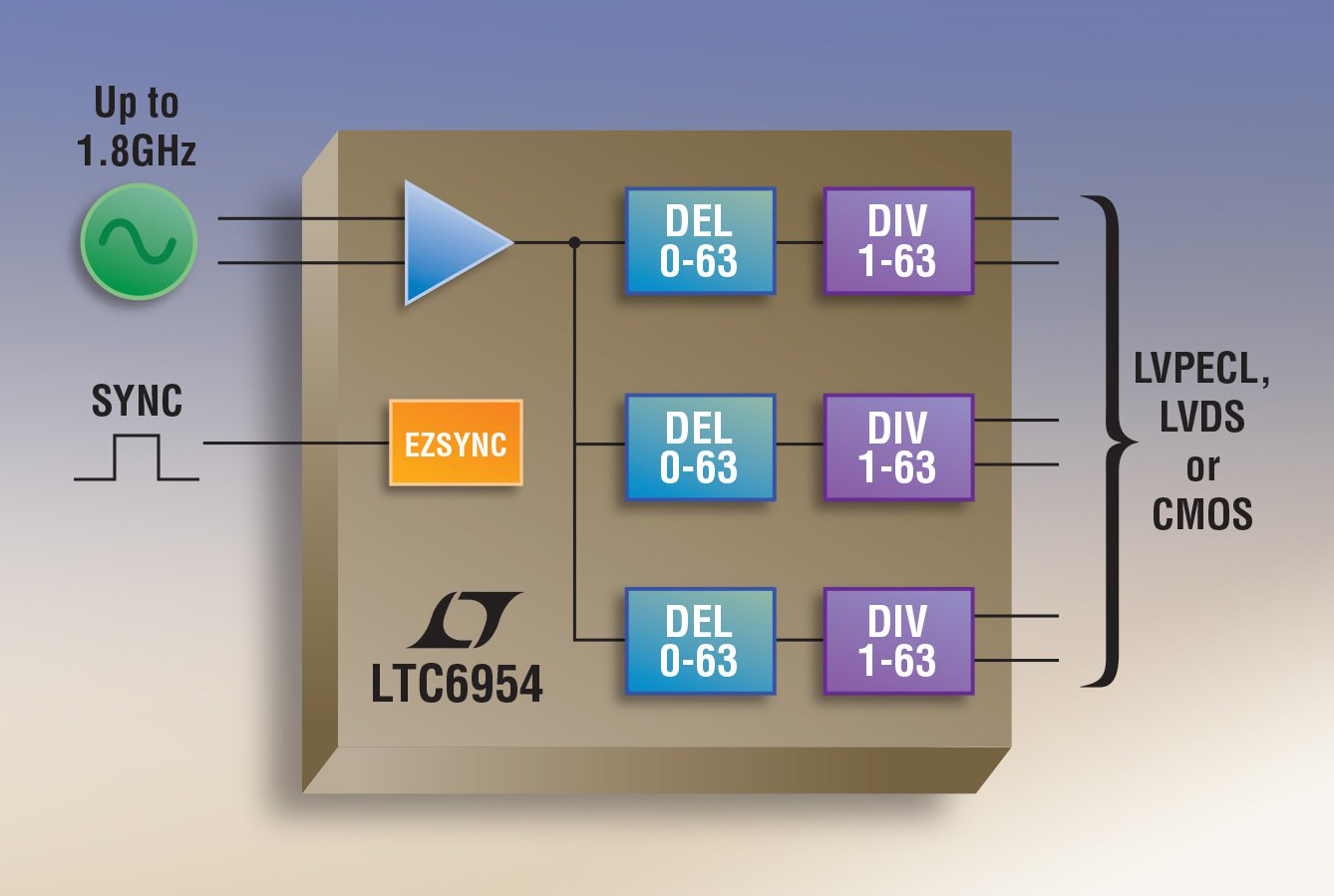

加利福尼亚州米尔皮塔斯 (MILPITAS, CA) – 2015 年 11 月 23 日– 凌力尔特公司 (Linear Technology Corporation) 推出超低抖动 1.8GHz 时钟分配芯片系列 LTC6954,该器件有 3 个独立的输出,每个都有自己的分频器和相位延迟。凭借在 12kHz 至 20MHz 带宽内不到 20fsRMS 的附加抖动,LTC6954 在对输入时钟进行分频和分配的同时,可最大限度减少了引入的噪声。这使 LTC6954 能够提供抖动很低的时钟,在驱动高分辨率数据转换器时,必须用这样的时钟才能实现最佳信噪比 (SNR)。例如,在对 RF 或高 IF 高频模拟信号等进行数字化时时,低抖动 ADC 时钟尤其重要,这使 LTC6954 成为这类系统中的理想时钟解决方案。

LTC6954 系列包括 4 个版本的器件,提供了各种不同组合的 LVPECL 和 LVDS/CMOS 输出逻辑驱动。这样就可以灵活地以最优方式连接到大量接受不同逻辑信号的器件。LTC6954 用单一 3.3V 电源供电,通过 SPI 设定,以 1 至 63 范围内的任何整数独立地对输入时钟分频,还能够以 0 至 63 个输入时钟周期独立地延迟每一路输出。这为建立必要的相移时钟提供了方便,例如,在通信系统中驱动 I 通道和 Q 通道的 ADC。

除了能够作为独立的时钟分配器使用,LTC6954 还采用了凌力尔特专有的 EZSync™ 同步方法。EZSync 同步由一个简单脉冲触发,使来自一个或多个芯片的多个输出对准上升沿,以在所有时钟分频器输出之间产生可重复和确定性的相位关系。LTC6954 可以作为跟随器与 LTC6950 配对使用,以增加由 LTC6950 产生的低抖动边沿对准时钟输出的数量。

LTC6954 在 –40°C 至 105°C 的整个工作结温范围内进行了规定,采用 4mm x 7mm 36 引线塑料 QFN 封装。该器件已经投产,千片批购价为每片 7.50 美元。

照片说明:附加抖动不到 20fsRMS 的时钟分配器

性能概要:

· 低噪声时钟分配以适合高速 / 高分辨率 ADC 时钟

· 附加抖动 《 20fsRMS (12kHz 至 20MHz)

· 附加抖动 《 85fsRMS (10Hz 至奈奎斯特频率)

· 1.8GHz 最高输入频率 (LTC6954-1,当 DELAY = 0 时)

· 1.4GHz 最高输入频率 (LTC6954-1,当 DELAY 》 0;LTC6954-2、-3、-4)

· 与 EZSync 时钟同步兼容

· 三个独立的低噪声输出

· 可提供 4 种输出组合

· 三个独立的可编程分频器,涵盖 1 至 63 的所有整数

· 三种独立的可编程延迟,涵盖 0 至 63 的所有整数

· –40°C 至 105°C 结温范围