当前VLSI 技术不断向深亚微米及纳米级发展,模拟开关是模拟电路中的一个十分重要的原件,由于其较低的导通电阻,极佳的开关特性以及微小封装的特性,受到人们的广泛关注。模拟开关导通电阻的大小直接影响开关的性能,低导通电阻不仅可以降低信号损耗而且可以提高开关速度。要减小开关导通电阻,可以通过采用大宽长比的器件和提高栅源电压的方法,可是调节器件的物理尺寸不可避免地会带来一些不必要的寄生效应,比如增大器件的宽度会增加器件面积进而增加栅电容,脉冲控制信号会通过电容耦合到模拟开关的输入和输出,在每个开关周期其充放电过程中会消耗更多的电流,时间常数t=RC, 充放电时间取决于负载电阻和电容,使得开关的速度变慢,同时增大宽长比也增加了器件的成本。当前减小导通电阻的普遍办法是提高开关管的栅电压。

1 传统模拟开关原理及栅增压原理

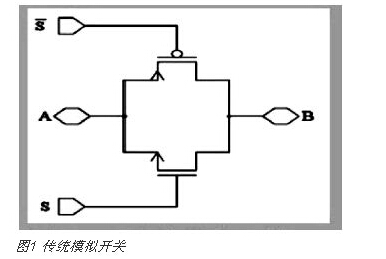

端分别为传送信号的输入、输出端,两个管子的栅极分别由极性相反的信号来控制。由于MOS管的源极和漏极可以互换,因此这个电路的输入、输出端也可以互换,它可以控制信息双向流通,就像一个双向开关。工作过程:当控制信号S=1 时,PMOS 管和NMOS管均导通,传输门接通,信号畅行无阻;当控制信号S=0 时,PMOS 管和NMOS 管均截止,传输门关闭,开关断开。当一管的导通电阻减小,则另一管的导通电阻就增加。由于两管是并联运行,可近似地认为开关的导通电阻近似为一常数。这是CMOS 传输门的优点。

1.1 模拟开关分析

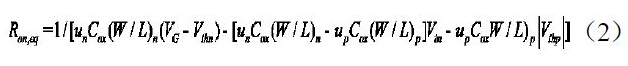

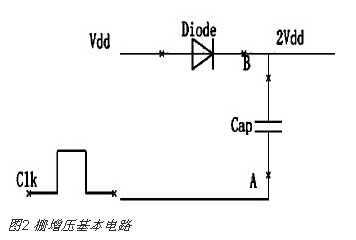

CMOS 开关的导通电阻为:

展开为:

其中un 和up 表示NMOS 管和PMOS 管迁移率;Cox 表示器件的栅氧化层电容;Vg 表示NMOS 管栅电压,Vthn|Vthp|分别表

示NMOS 管和PMOS 管的阈值电压,如果设计时取

时,式(2)可化简为:

导通电阻将不随输入信号改变而改变,可等效为一个恒定阻值的电阻,如式(3),不会引起模拟信号的失真,由于导通电阻是由两个电阻并联,所以阻值较单管开关小得多,使得开关速率又得到提高。从式(3)中可以知道MOS 开关为了能提高速度和精度,需要抬高NMOS 管的栅电压。增加栅电压最直接的办法就是提高电路的电源低压,但是从低电压系统角度来说这增加了成本,因此需要加一个电源电路,最好的办法是芯片内部产生一个电压来增加栅电压。

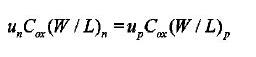

1.2 栅增压原理

栅增压原理是依靠电荷泵的工作原理:先贮存能量,然后以受控方式释放能量,以获得所需的输出电压。本文中所用的电容式电荷泵采用电容器来贮存能量,通过电容对电荷的积累,电容A 端接时钟信号Clk,当A 点电位为0 时,B 点电位为Vdd;当A点电位为Vdd 时,由于电容两端的电压不会突变,理想情况下,此时B 点电位被抬升为2Vdd,因为电荷泵的有效开环输出电阻存在,使得实际情况B 点电位低于2Vdd。

2 改进型模拟开关电路设计

2.1 电路描述和分析

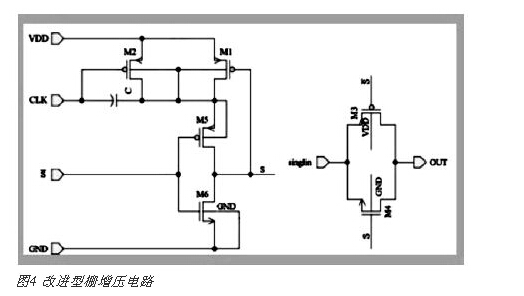

图4 为本文设计的栅增压电路,M3 和M4 组成了一对传输门,可以保证输入信号在高低电压无损失地传输到传输门的另一端。M1 的栅极接反相器的输出端,漏源两端分别接电容正极板和电源电压,M1 的作用是当开关连通且时钟信号为高电平时,保证电容电压抬升后不会迅速放电使电容正极板电位为0。M2 的栅极接时钟信号CLK,漏源两端分别接电容正极板和电源电压,它的作用是当开关关闭时,M2 导通时使电容正极板电位保持在电源电压。下面分析该电路的工作情况:

当开关关闭时,S 为低电平,M1 导通,保证电容正极板上的电压最低为VDD,此时M3 和M4 都不导通,信号不能达到输出端。当开关导通时,S 为高电平,M1 截止,时钟为低电平时,M2 和M5 导通,M1 和M6 关闭,电容充电至P-Vds;CLK为高时,由于电容两边电压不会突变,电容正极板上的电压会被抬升至原来的两倍。

从上面分析可知,所有跟开关栅端电压连通的电压都是和输入信号无关的,因此开关导通电阻与输入信号无关,可以大大抑制信号有关的电压损失,保证了信号的线性度和器件的可靠性。

2.2 性能仿真及结果分析

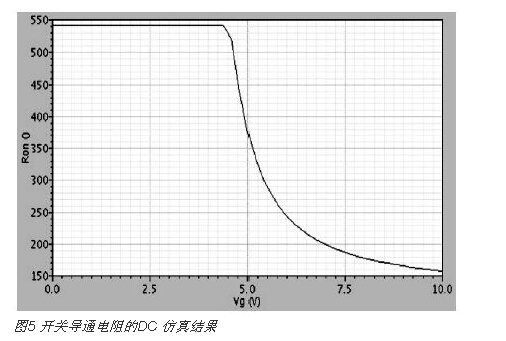

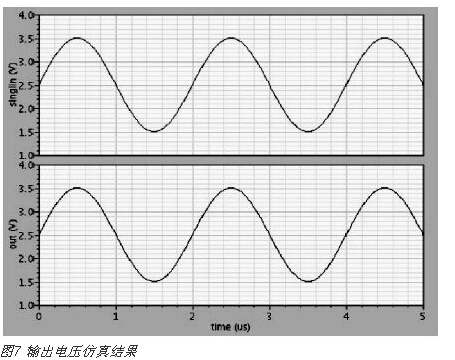

基于NEC0.35umCMOS 工艺的模型参数,采用Spectre 模拟软件,对图3 进行模拟仿真。电源电压为5V,输入信号singlin为500KHZ,信号幅度5V,电荷泵时钟为100MHZ,电容为1.8pf,仿真得到了开关导通电阻随Vg 电压的变化(图5)、电荷泵抬升后的电压(图6)和输出信号结果(图7),可见,导通电阻在大于电源电压时急剧降低,电容正极板上的电压可以抬升至9V,输出电压波形比较理图想,损耗很小,几乎没有。

3 结语

本文分析了CMOS 模拟开关对传输信号的影响。利用电荷泵技术,设计了一种5V 电源电压下的模拟开关,该器件适用于0~5V 的输入信号,并能将0~5V 的时钟信号抬升到0~10V,从而具有更好的线性特性和更小的导通电阻,大大降低信号的失真。对开关电路进行了分析,采用Spectre 软件,基于NEC0.35um CMOS 工艺条件进行仿真,验证了该结构的线性度和可靠性。