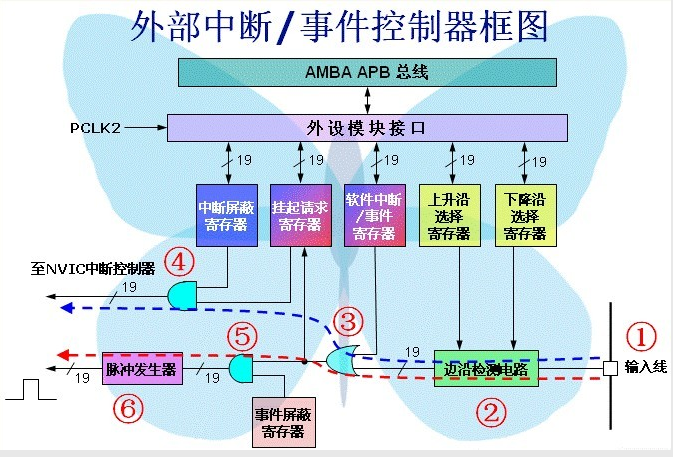

这张图是一条外部中断线或外部事件线的示意图,图中信号线上划有一条斜线,旁边标志19字样的注释,表示这样的线路共有19套。

图中的蓝色虚线箭头,标出了外部中断信号的传输路径,首先外部信号从编号1的芯片管脚进入,经过编号2的边沿检测电路,通过编号3的或门进入中断“挂起请求寄存器”,最后经过编号4的与门输出到NVIC中断控制器;在这个通道上有4个控制选项,外部的信号首先经过边沿检测电路,这个边沿检测电路受上升沿或下降沿选择寄存器控制,用户可以使用这两个寄存器控制需要哪一个边沿产生中断,因为选择上升沿或下降沿是分别受2个平行的寄存器控制,所以用户可以同时选择上升沿或下降沿,而如果只有一个寄存器控制,那么只能选择一个边沿了。

接下来是编号3的或门,这个或门的另一个输入是“软件中断/事件寄存器”,从这里可以看出,软件可以优先于外部信号请求一个中断或事件,既当“软件中断/事件寄存器”的对应位为“1”时,不管外部信号如何,编号3的或门都会输出有效信号。一个中断或事件请求信号经过编号3的或门后,进入挂起请求寄存器,到此之前,中断和事件的信号传输通路都是一致的,也就是说,挂起请求寄存器中记录了外部信号的电平变化。外部请求信号最后经过编号4的与NVIC中断控制器发出一个中断请求,如果中断屏蔽寄存器的对应位为“0”,则该请求信号不能传输到与门的另一端,实现了中断的屏蔽。明白了外部中断的请求机制,很容易理解事件的请求机制了。图中红色虚线箭头,标出了外部事件信号的传输路径,外部请求信号经过编号3的或门后,进入编号5的与门,这个号4的与门,用于引入事件屏蔽寄存器的控制;最后脉冲发生器把一个跳变的信号转变为一个单脉冲,输出到芯片中的其它功能模块。

在这张图上我们也可以知道,从外部激励信号来看,中断和事件是没有分别的,只是在芯片内部分开,一路信号会向CPU产生中断请求,另一路信号会向其它功能模块发送脉冲触发信号,其它功能模块如何相应这个触发信号,则由对应的模块自己决定。在图上部的APB总线和外设模块接口,是每一个功能模块都有的部分,CPU通过这样的接口访问各个功能模块,这里就不再赘述了。