摘要:随着电子通信以及教学事业的发展,示波器的应用越来越广泛,它在教学中所起到的作用越来越重要,示波器可以测量信号的幅度,频率以及波形等等,但是高精度的示波器非常昂贵,对于非盈利事业的教学组织来说无疑不合适,所以提出了一种以单片机为控制核心的简易示波器设计方案。它由前向控制部分,数据采集和存储部分,51单片机控制部分以及按键和MS12864R显示部分组成。

传统意义上的模拟示波器虽然功能较全,但是价格昂贵,体积大、重量重、成本高、等一系列问题使应用受到了限制。对于大多数学生以及教学组织来说,利用示波器主要是进行一些理论性的测试与实验,高精度高成本示波器的作用不是很必要,为此,笔者提出了一种便携式数字存储示波器的设计,它采用了LCD显示、高速A/D采集与转换、FIFO以及单片机等技术,具有较强的实用性以及发展的市场潜力,前景可观。

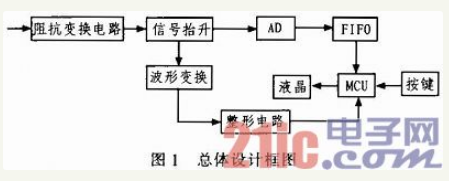

1 简易数字示波器的工作原理以及总体框架

本设计硬件电路部分由单片机控制系统电路,前向输入调理电路,模数转换和存储电路,以及按键显示电路组成。其工作的基本思路就是以单片机为控制核心,让AD芯片完成数据的离散化,采集数据经过缓冲暂存于存储器里面,当波形显示时,单片机从存储器的读使能端读取采集数据存于数组中,然后进行相应的数据处理并把所存取得数据按一定的顺序打在液晶显示器相应的位置上,从而再现波形信号;其中输入调理电路由阻抗变换电路,信号抬升电路以及频率测量电路构成,阻抗变换电路是为了提高输入阻抗,信号抬升是为了使信号的幅度满足AD芯片的输入幅度要求,频率测量电路主要是测量周期性信号的频率。总体设计框图如图1所示。

2 硬件设计

2.1 前端信号的处理

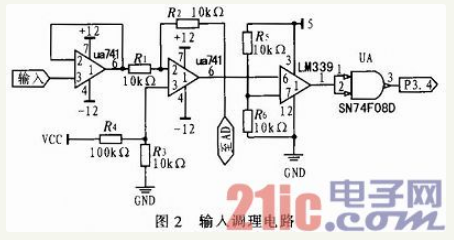

本模块具有两大功能,一是输入信号位置的变换;二是信号波形的变换。

信号位置的变换主要由阻抗变换电路,信号抬升电路构成,阻抗变换采用ua741构建的阻随放大电路,信号抬升电路采用ua741构成的加法电路,信号位置的处理主要是对被测输入信号在幅度与偏移方面进行线性处理,使信号在垂直方向上处于A/D转换器的输入范围内。波形变换电路是用来测量输入信号的频率,但是单片机属于数字器件,为此,我们需要对输入信号进行波形变换以及脉冲整形;硬件电路设计如图2所示。

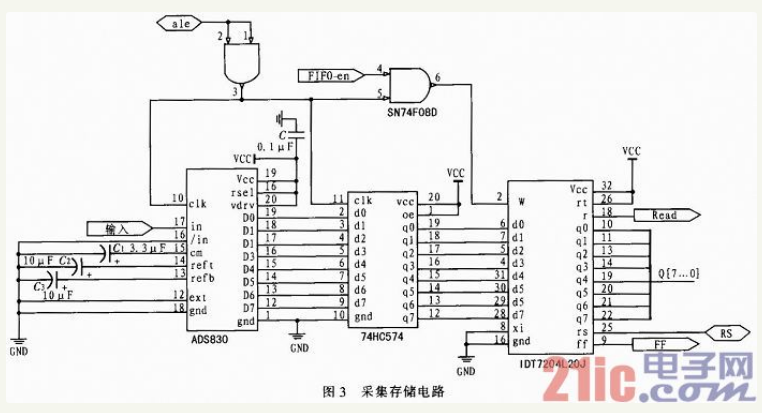

2.2 信号的采集与存储

数据采集部分㈣是本设计的核心部分,本设计采用BB公司的8位AD,试验中让AD完成数据采集,采集完数据送往FIFO,通过FIFO中继再送往单片机,FIFO是一种双口RAM,它没有地址线,随着写入数据或者读取数据而使地址指针进行递增或者递减来实现寻址,两者中间接了一个缓冲器,这样可以起到数据缓冲作用,在MCU与AD之间接入FIFO的作用是起到数据缓冲的作用,因为AD的时钟高于MCU的工作频率,所以让AD和FIFO同步工作来存储AD转换的输出数据,实验中AD与FIFO的时钟同步,来自于ALE引脚,为了使时钟更加稳定,可以让ALE信号先经过与门再送往采集存储模块;FIFO有3个标志位引脚,FF满标志,HF半满标志以及EF空标志,本设计只利用了FF满标志,当FIFO存满时通知单片机来读取数据,这是单片机使FIFO的写使能禁止,只来读取数据以显示,硬件电路设计如图3所示。

2.3 液晶显示

试验中波形的显示是借助Ms12864R,采用8位并行数据处理,利用了液晶的打点功能,数据采集的先后顺序体现在液晶的横轴上面,也就是波形显示的时间先后,而数据值的大小则体现在液晶的纵轴上面,也就是波形的幅度体现。

由于采用FIFO,所以先采样的点后显示,这是波形显示的核心,如图4所示。12864主要有4个编程端口,RS(数据命令选择),RW(读写选择),EN(使能端)以及PSB(串并选择),电路连接中分别接到单片机的某一I/O口上。

2.4 按键电路

本设计需要按键较少,因为设计要求X方向能够设置10us/p,20us/p,40us/p三档水平扫描速度,Y方向能够设置0.5V/p、1V/p二档垂直灵敏度,加之幅度和频率的测量,所以本设计要6个独立按键就够了。

3 软件部分

3.1 总体程序框图

总体程序框图如图5所示。

3.2 测量频率流程图

测量频率流程图如图6所示。本设计频率测量是基于计数法和测周期法混合使用。其基本思想就是先测量1 s内被测信号的上升沿个数,来一个上升沿计数器加1,为了防止计数器产生溢出,设计中将1 s分成20个50 ms,中断20次,测出信号频率,如果频率值小于1K,则改用测周期法。

3.3 液晶打点流程图

打点操作是作图的基础,由于st7920控制器的绘图RAM是一次进行两个2个字节的数据的读写操作,也就是一次修改的是16个点的状态,而我们要想只修改一个点的状态同时不改变其余相邻15个点的状态,那只能是先把原来位置的16个点的状态读出,使用位操作指令修改其中一个点的状态,然后在回写到RAM中。整体的过程即是:读取-修改(位状态)-写入。液晶画点是编程的难点与重点,需要把液晶纵向每隔转换为电压,要把水平方向转化为时间,将波形显示出来,其步骤如下:先确定打点的位置;其次读出该点所在的数据值;接着修改该点相应的位的值,对于单色液晶来说,只有两种操作,一是点亮该点,另一种是熄灭该点;最后将修改后的数据值写入对应的地址。打点流程图如图7。

3.4 测试结果

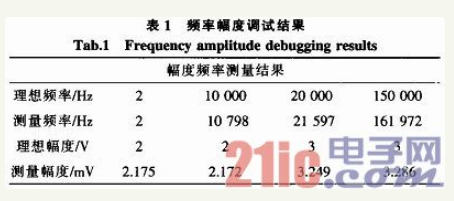

波形测试结果(波形之一,其他略)频率幅度测试结果如表1所示。

4 结束语

本系统按照功能全面,指标合理,总体价格低廉的要求设计了硬件电路,充分地利用了单片机的I/O接口,使之成功地实现了频率的测量,信号幅度的测量,以及不同灵敏度波形的显示。而且幅度频率测量误差较小,显示波形没有明显的失真,满足设计要求。如果利用高端控制器,则可以实现高精度的测量,前景远大,很有研究价值。