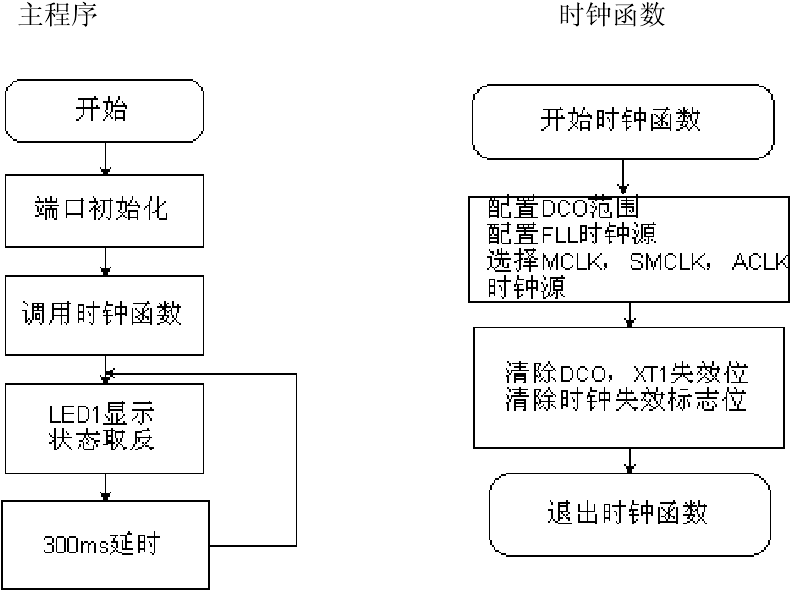

2,编程要求:编成完成 SMCLK,MCLK,ACLK 按指定频率进行输出,FLL+源自 RERO

3,实现功能:ACLK = REFO , MCLK = ~2MHz,SMCLK = ~1MHZ

4实验现象:ACLK 接近 32768 稍有偏差,MCLK = ~2MHz,SMCLK = ~1MHZ,LED1 不停闪烁

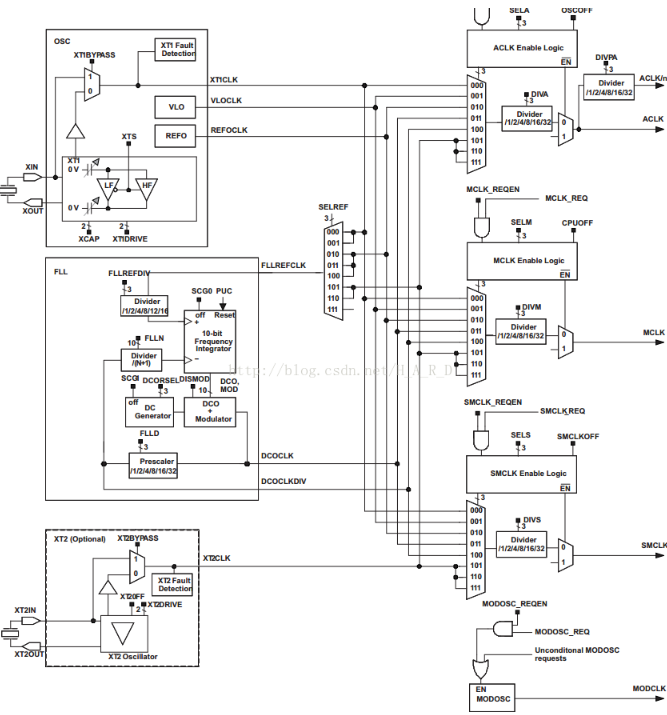

1MSP430F5438 时钟系统介绍时钟源

UCS 模块是一个低成本低功耗的时钟系统。包含有多个时钟源和时钟信号,用户可以自行配置,得到性能和功耗的最佳平衡点。 UCS 软件配置后,只需要外部一两个晶振或者电阻,而不需要其他的任何器件。

UCS 模块最多含有 5 个时钟源:

XT1CLK :低频 /高频振荡器,可以使用低频 32768HZ 钟振、标准晶振、外部振荡器或者通过外部输入源输入 4MHZ~32MHZ 时钟。 XT1CLK 可以作为内部 FLL 模块的参考时钟,有些器件只支持外部的低频晶振,具体可参考数据手册。

VLOCLK :内部低功耗,低频振荡器。典型值为 10KHZ 。

REFOCLK :内部低频振荡器,典型值为 32768HZ ,作为 FLL 基准时钟源。

DCOCLK :内部数字控制振荡器 (DCO) 可以通过 FLL 来稳定。

XT2CLK :可选择的高频振荡器,可以使用标准晶振,振荡器或者外部时钟源输入4MHZ~32MHZ 。

时钟信号:

UCS模块可以提供三个时钟信号:

ACLK :辅助时钟。 ACLK 可由软件选择来自于 XT1CLK ,REFOCLK ,VLOCLK ,DCOCLK ,DCOCLKDIV ,和 XT2CLK (如果可以用) 。DCOCLKDIV 为 DCOCLK在 FLL 模块中通过 1、2、4、8、16、32 分频后得到的频率。 ACLK 可由软件配置位各个模块的时钟信号。 ACLK 可由 1、 2、4、8、16、32 分频后使用。 ACLK/n是 ACLK 经 1、2、 4、8、16、32 分频后通过 IO 口输出作为外部电路使用。

MCLK :系统主时钟。 MCLK 可由软件选择来自于 XT1CLK ,REFOCLK ,VLOCLK ,DCOCLK , DCOCLKDIV , XT2CLK (如果可以用) 。 DCOCLKDIV 为 DCOCLK在 FLL 模块中通过 1、2、4、8、 16、32 分频后得到的频率。 MCLK 可以通过 1、2、 4、 8、 16、 32 分频后使用。 MCLK 可以作为 CPU 和系统时钟。

SMCLK :子系统主时钟。 SMCLK 可由软件选择来自于 XT1CLK , REFOCLK ,VLOCLK , DCOCLK , DCOCLKDIV ,XT2CLK (如果可以用) 。 DCOCLKDIV 为DCOCLK 在 FLL 模块中通过 1、2、4、 8、16、 32 分频后得到的频率。 SMCLK 可以通过 1、2、4、8、16、32 分频后使用。 SMCLK 主要用于高速外围模块。

2实验原理

F5XX 单片机有更加丰富的时钟系统,内部有 XT1,XT2,REFO,VLO,DCO,MODCLK,并且ACLK,MCLK,SMCLK 时钟源选择更加丰富,并且都可以经过分频处理,F5XX 时钟系统框图如图 。

3寄存器设置

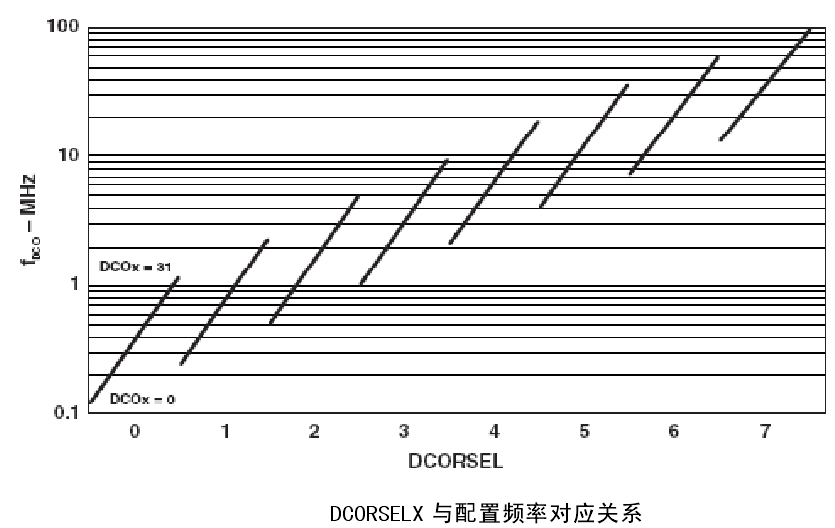

F5XX 系列的时钟 MCLK ,SMCLK ,ACLK 均可以选择 XT1,REFO XT2 时钟源,时钟配置寄存器丰富,用户可以根据需要设置相应得寄存器,来输出用户需要的频率。由于 DCO 是由 RC 电路组成频率输出电路,因此需要调节,DCORSELX 提供用户满足需要的标称频率,可以理解为一个粗调。因此用户在调节频率过程中必须要正确配置该位,否则配置不当会造成 DCO 时钟失效,DCORSELX 与配置频率对应关系如图 。

在默认状态下 XT1 是关闭状态的,如果模块时钟选择 XT1 提供时钟源,那么系统内部时钟REFO 就会暂时替代 XT1 提供时钟,但是 REFO 精度和稳定性XT1 要差,因此要求比较高场所建议使用 XT1.如果将 XIN,XOUT 引脚设置为特殊引脚,那么晶体就会起振。XT1DRIVE1 设置在为 0 的时候低驱动能力,将 XT1 失效,XT1 停止振荡。

例如将时钟配置为 MCLK = SMCLK =2MHZ,ACLK =XT1

P7SEL |= 0x03; // XT1 起振

UCSCTL1 = DCORSEL_2; // 选择 DCO 范围

UCSCTL4 = SELM_4 + SELA_0 + SELS_4; //MCLK =MCLK =DCO,ACLK=XT1

while (SFRIFG1 & OFIFG) //清除 OFIFG,XT1OFFG ,DCOFFG

{

UCSCTL7 &= ~( XT1LFOFFG + DCOFFG);

SFRIFG1 &= ~OFIFG;

}

4实验代码

5实验流程

6注意

UCS 配置需要注意一下方面:

1.在默认状态下 XT1 是关闭状态的,如果模块时钟选择 XT1 提供时钟源,那么系统内部时钟 REFO 就会暂时替代 XT1 提供时钟,但是 REFO 精度和稳定性比 XT1要差,因此要求比较高场所建议使用 XT1.如果将 XIN,XOUT 引脚设置为特殊引脚,那么晶体就会起振。

2.DCORSELX 的配置与设置的频率要保持统一,如果不统一就可能出现 OFIFG 为 1,或者频率数值达不到所需要的频率值大小。

3.XT1DRIVE1 设置在为 0 的时候低驱动能力,将 XT1 失效,XT1 停止振荡