普通门电路,对输入信号是被动传输的。而可控门电路,则有一定的主动权,输入信号到了“门口”,是放行(正常传输),还是阻止(处于阻断状态),则由开、关门控制信号说了算。说白了,这种可控门,起码有两种状态,“开门”和“关门”状态。相对于普通门,多一个“关门”状态。

对此种数字电路的定义概念较多,如题目括号中所示。其输出级电路具三态特性。何谓三态?需从数字电路芯片的输出级结构来谈起。

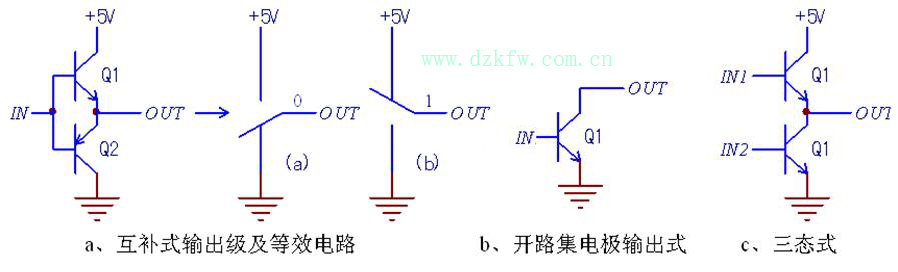

图1 数字门电路输出级的三种结构形式

普通数字门电路的输出级电路,常用a电路形式,因内部Q1、Q2仅工作于饱和和截止两种工作状态,电路实质上相当于一刀两掷的高、低电平切换开关,要求接通电阻越小越好(传输电压信号时可忽略接通电阻/电压降),无论输出高、低电平,均为低阻状态。

b电路形式(开路集成极输出),称为高电压大电流器件,具备一定的功率驱动能力,如可以直接驱动继电器,典型器件如ULN2003A等,而外部负载电源可以另供为高电压(如24V或48V),以适应负载电源电压要求。

c电路形式,则除了高、低电平的低阻状态,还存在第三种状态:高阻态。如图2所示。

图2 三态式输出级的三种工作状态

其输出级Q1、Q2基极输入的是两路独立电平信号:

a态:当Q1导通时,相当于输出端与+5V接通,输出为高电平(低阻态1);b态:Q2导通时,输出端相当于与供电地接通,输出为低电平(低阻态2);c态:当控制信号俱为0时,Q1、Q2均处于截止状态,此时OUT输出端相当于“悬空”——高阻态(与内部电路失掉联系)。有两个问题:

1、处于高阻状态时,检测OUT端应该为什么电平?高阻态有何意义?

这与电路设计者的考虑——后级电路的输入要求相关。处于高阻态时,其输出电压状态的高、低完全由设计者决定——由接入偏置(上拉、或上拉电阻)电路来决定之。

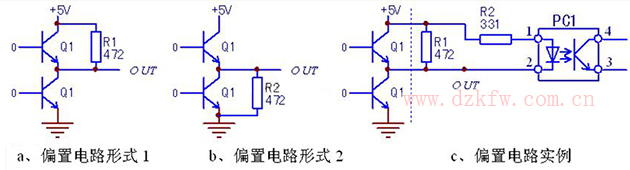

图3 三态式输出级的三种工作状态

a电路,在高阻态其输出端取决于R1电路形式,为5V高电平。此高电平内部电路无关;b电路,在高阻态则由R2的下拉作用,使输出端为低电平,同样与输出级电路无关;c电路,为一个偏置电路实例,当电路设计要求在静态时,光电耦合器PC1处于截止状态,电路的安全性能更有保障时,接入R1上接电阻,使电路静态时,PC1无导通条件,显然更为合理和可靠。

因而电路的第三态——高阻态的出现,其意义如下:

1)可由设计者任意决定输出的高、低电平状态(与输出信号无关);

2)当多组器件输出端需要并联(如信号总线模式)时,只有“需要动作”的器件工作模式为高、低电平(指低阻)态,而“闲置”电路,则处于高阻态,从而不会影响总线电平,不会影响有用信号。

2、什么情况下输出端会进入高阻态?三态门与普通门的区别?

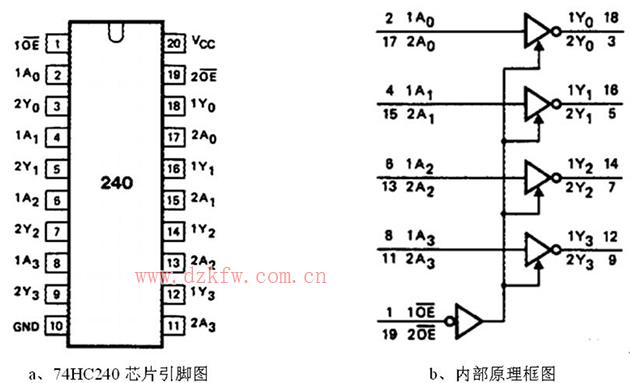

以74HC240电路(八反相缓冲器/线驱动器/线接收器)为例加以说明。

图4 74HC240芯片引脚图,74240内部原理框图

从上图可看出,芯片内含8路反相器电路,与普通反相器电路相比较,每路反相器除输入、输出端外,多出一个OE控制端。当OE端为低电平时,电路处于“开门”即通态,相当于普通反相器的功能;当OE端为高电平时,传输状态被阻断,输出端处于高阻状态。

显然,与普通门电路相比,可控门(为反相器或同相器)电路,多出一个OE控制端——“开、关门”信号输入端。信号的传输不但与输入信号状态相关,而且与OE控制端的状态相关。

以74HC240为例,当信号传输异常时,对可控门的故障检修需注意:

输入信号无,查前级电路;

控制端是否有“关门”信号存在,即1、19脚是否变为高电平?是,查OE端控制信号来源;

芯片本身损坏。当输入信号与控制端电平状态都正常时,落实至芯片本身。

常见三态同相/反相可控门电路型号为74HC240(八反相可控门)、74HC244(八同相可控门)、74HC365(六同相可控门)、75HC366(六反相可控门)。以74HC240为例:该器件斜对角10、20脚为电源引脚,除信号输入、输出引脚外,尚有两个OE控制端(1、19脚),每个OE端分别控制四路反相器电路的开、关门。

通常,普通门与三态门为基本逻辑电路,在些基础上,将普通门电路进行有序搭接,可组成复杂的组合型逻辑电路。近年来,MCU、DSP、PIC和JTAG等器件技术的完善,在一定程度上取代了组合逻辑电路(完成同一逻辑功能,采用MCU更为简洁,用软件方法即可完成——用程序行来代替了大片的硬件数字信号处理电路)。