LED显示屏是利用LED点阵模块或像素单元组成的一种现代平面显示屏幕,具有发光效率高、使用寿命长、视角范围大、色彩丰富以及对室内外环境适应能力强等优点。目前的LED显示屏控制系统多采用ARM处理器来完成整个系统的功能,这种控制系统在数据处理速度上存在很大的局限,影响显示效果的连续性。基于此,在分析了STM32微处理器总线结构特点的基础上,提出了STM32+FPGA的控制系统方案,该方案充分了利用STM32微处理器的灵活的储器控制技术和可编程逻辑器件的灵活性,提高了系统数据处理的速度,而且简化了电路结构,方便调试。

1、系统总体方案设计

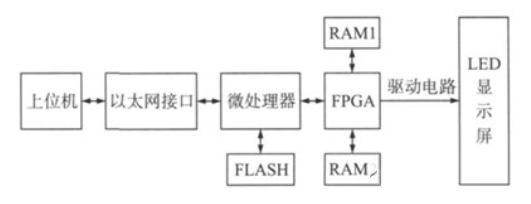

系统结构框图如图1所示。

图1 系统结构框图

系统采用新一代的32bitRISC处理器STM32作为主控芯片,通过以太网传输数据,以FLASH作为存储模块,由FPGA完成对LED显示屏的高速扫描刷新。系统工作时,利用上位机编辑显示信息,通过以太网接口将显示信息传输给微处理器,微处理器接收数据信息后写入FLASH存储器。在显示时,微处理器读取FLASH中的数据,通过总线将数据以并行方式发送给FPGA,FPGA处理后将数据传输到LED显示屏显示。

2、系统硬件设计

本系统选用ST公司新推出的32位微处理器STM32F103ZET6作为主控芯片,STM32F103ZET6使用了先进架构的ARMCortex-M3内核,其灵活的静态存储器控制器使得它能很方便的和许多存储器和外设连接,同时STM32片上外设丰富,可以简化系统外围电路的设计。

2.1、FLASH存储器电路设计

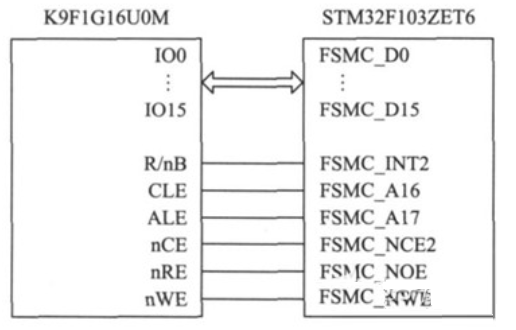

FLASH采用的是三星公司的K9F1G16U0M,它是一种NAND型FLASH,存储容量为64M16位,工作电压3.3V,系统中STM32F103ZET6与K9F1G16U0M的连接如图2所示。FLASH存储器的IO0~IO7和FMSC数据总线的低8位相连,STM32处理器通过FSMC访问存储器;FLASH存储器的片选信号nCE和FSMC的FSMC_NCE2相连接,这样存储器的地址空间为0x70000000~077FFFFFFFF;FLASH存储器的R/nB连接至STM32处理器的FSMC_NWAIT管脚,处理器将R/nB作为一个中断源使用,因此可以在存储器的等待周期内执行其他的任务。

图2NANDFLASH与STM32F103ZET6连接图

2.2、以太网接口电路设计

采用以太网接口代替传统的串口,加快了数据传输的速度,同时可以实现远程控制。由于STM32F103ZET6片内没有集成以太网MAC和PHY功能,但其FSMC支持扩展以太网控制芯片,本系统在FSMC上扩展一片DAVICOM公司的DM9000A芯片对STM32F103ZET6进行以太网扩展,DM9000A与STM32F103ZET6的连接如图3所示。

图3 DM9000A与STM32F103ZET6连接图

STM32F103ZET6通过FSMC访问DM9000A,对于STM32F103ZET6来说,DM9000A就是一个静态存储器外设。DM9000A采用16位模式,数据线SD0~SD15直接与FMSC数据线低16位FSMC_D0~FSMC_D15相连;DM9000A片选信号线nCS连接至FSMC片选信号FSMC_NE4,这样DM9000A端口地址为0x6c000000;DM9000A的中断信号线INT可直接连接至STM32F103ZET6的IO口,在程序中激活处理器IO口的中断复用功能,STM32以中断方式接收网卡数据。

2.3、扫描驱动电路设计

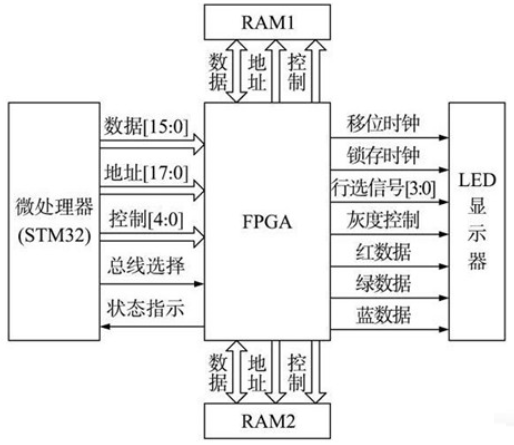

扫描驱动电路是整个控制系统的重要组成部分,系统中它由一块FPGA和双体RAM组成,其结构如图4所示,主要完成灰度数据读取、上屏数据的产生与传输、移位和锁存时钟的产生、行选信号的产生、灰度控制信号的产生等功能。

图4 扫描驱动电路结构图

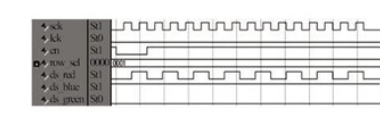

扫描驱动输出信号的仿真波形如图5所示,其中en是灰度控制信号,用来控制显示时间,产生灰度效果;row_sel是行选信号,显示时用于确定点亮哪一行;sck是移位时钟,lck是锁存时钟,ds_red、ds_blue、ds_green是上屏红、蓝、绿数据的输入端。仿真时红、蓝、绿显示数据分别设定为01交错、全1、全0。可以看到,在移位时钟的作用下数据移位正确,移位完成后,lck变为高电平,将数据锁存输出到LED屏上显示。

图5 输出信号的仿真波形

3、系统软件设计

整个系统的软件包括3个部分:上位机应用软件、微处理器控制软件和FPGA控制软件。3个部分协同工作,实现对LED显示屏的控制。

3.1、上位机应用软件

上位机应用软件用于人机交互,是控制系统对用户的接口,要求界面友好、操作简单。软件采用VisualC++编写,完成的主要功能包括:图像文字信息的编辑、图像的解码以及根据通信协议将数据发送给下位机。

3.2、微处理器控制软件

微处理器在整个系统中起着核心调度的作用,它控制着系统各功能模块的工作状态,程序包括TCP/IP协议栈的移植、DM9000A网卡驱动程序等,完成的主要功能有:硬件初始化,上位机与下位机的以太网通信,显示模式算法设计等。

3.3、FPGA控制软件

FPGA控制软件的设计是在QuartusII环境下完成的,采用硬件描述语言Verilog编写。主要功能是根据微处理器的控制,对存储器进行切换,实现乒乓操作;完成图像数据的重构,把数据转换为能直接用于LED扫描显示的含有灰度信息的0和1组成的编码系列,并根据显示屏驱动芯片的时序,将编码系列传输到显示屏上显示。

4、总结

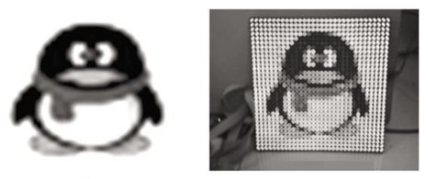

本设计采用32位嵌入式微处理器STM32F103ZET6和可编程逻辑器件EP1C6Q240C8设计了全彩色LED显示屏控制系统,并在实验室验证,实现了LED显示屏的彩色显示,图6(a)为一幅实际图像,图6(b)是在显示屏上的显示效果。

图6 图像的灰度显示

实验结果表明,系统运行稳定,显示画面清晰、流畅。系统该系统能满足异步全彩色LED显示屏高处理速度,大容量数据存储的要求,支持256灰度级全彩图像、动画的显示,同时通过改变FPGA内部的硬件逻辑可方便地对系统进行升级,结构简单、可靠性高,可替代市场上同类设计产品,应用前景广泛。