由于计算机内部的主要工作过程是信息传送和加工的过程,因此在机器内部各部件之间的数据传送非常频繁。为了减少内部的传送线并便于控制,通常将一些寄存器之间数据传送的通路加以归并,组成总线结构,使不同来源的信息在此传输线上分时传送。

根据总线所在位置,总线分为内部总线和外部总线两类。内部总线是指CPU内各部件的连线,而外部总线是指系统总线,即CPU与存储器、I/O系统之间的连线。本节只讨论内部总线。

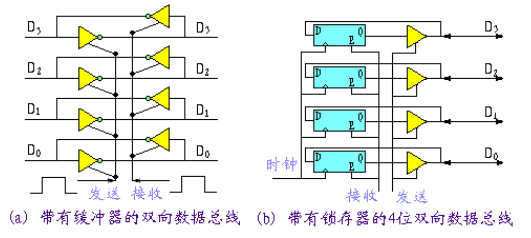

按总线的逻辑结构来说,总线可分为单向传送总线和双向传送总线。所谓单向总线,就是信息只能向一个方向传送。所谓双向总线,就是信息可以分两个方向传送,既可以发送数据,也可以接收数据。

图2.14(a)是带有缓冲驱动器的4位双向数据总线。其中所用的基本电路就是三态逻辑电路。当“发送”信号有效时,数据从左向右传送。反之,当“接收”信号有效时,数据从右向左传送。这种类型的缓冲器通常根据它们如何使用而叫作总线扩展器、总线驱动器、总线接收器等等。

图2.14由三态门组成的双向数据总线

图2.14(b)所示的是带有锁存器的4位双向数据总线。它主要由一个DE触发器和一个三态缓冲器组成。DE触发器是在一个普通D触发器上另加一个E输入端(允许端)而构成的。此处E输入端用以控制D的输入。若E=0,即使D为“1”,也不能输入。当接收数据时,E=1三态门被禁止,因而数据总线上的数据被接收到锁存器。当发送数据时,E=0,三态门被允许,因而锁存器的数据发送至数据总线上。