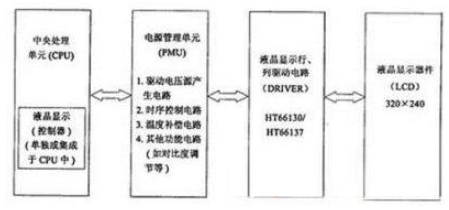

对于分辨率较小的液晶显示器件,如128&TImes;64、128&TImes;32等模块都具有控制器、电源管理单元、驱动器于一体的芯片。但对于高分辨率的液晶显示器(如320&TImes;240 ,640&TImes;480) 需要单独的控制器、电源管理单元、驱动器。本文给出了一种高分辨率液晶显示器电源管理电路的设计方案。

图1:液晶显示系统4个单元框图

驱动电压产生电路

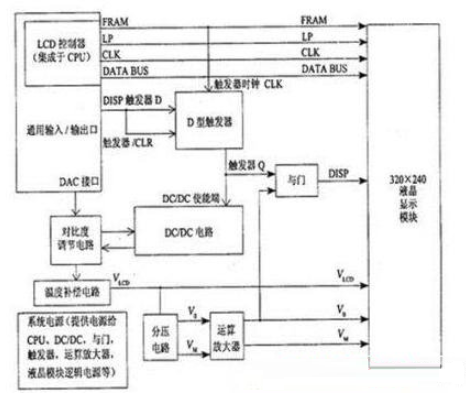

液晶显示不仅需要逻辑电源,而且要有驱动电源。驱动电源因驱动芯片的不同而异,本文以日本日立公司HT66130/ HT66137为例。该系列芯片是驱动高分辨率液晶显示器的芯片,所需驱动电压为VLCD 、V0 、VM3种。由于占空比达1/240 ,VLCD电压达15V以上,我们选用美信公司的DC/DC器件MAX1606产生15.9V的VLCD电压,经电阻分压得到V0 和VM ,V0 和VM再经运算放大器提供给HT66130和HT6613,如图2所示。

图2:液晶显示电源管理框图

时序控制电路

所有液晶显示器对于上电、下电时序都有严格要求。如果上电、下电时序不符合要求,则不能正常显示,常常会出现乱码、锁存、残留显示等现象。以日本日立公司驱动芯片HT66130/HT66137驱动320×240液晶显示屏为例,对上电、下电时序的要求如图3所示,一般液晶显示驱动芯片要求也大致如此。

通常液晶显示器的电源管理电路是依靠CPU用软件来控制信号的时序,以保证液晶显示器件对上电、下电时序的要求。这就占用更多的通用输入、输出口(GPIO),而且对于上电瞬间软件尚未运行起来,只能依靠CPU的GPIO的默认状态来控制。目前智能手机等双CPU系统更不易依靠软件来实现控制。本文设计的电路仅需一个GPIO(即显示使能信号DISP) ,就可以控制上、下电时序及驱动电源的开关,而且对DISP无任何时序要求。

图3:日立公司HT66130/HT66137时序图

对上电时序,一般必须有一帧频初始化时间后,才可置显示使能信号为高电平。传统做法是依靠CPU的GPIO口延时来控制。本文设计的电路利用D型触发器,并以帧频信号(FRAME)为时钟输入,以显示使能信号(DISP)为D输入并控制CLEAR端,Q端输出控制整个驱动电路的开关。这样既可以实现DISP输入的时序控制,又可以用DISP控制整个驱动电源电路的开关。由于DISP可关掉驱动电路,所以可以实现待命状态驱动电路功耗很小,仅有触发器和门电路的静态电流。为了满足驱动电压稳定后DISP信号输入,我们采用与门控制DISP与驱动电压输入来实现DISP输出。

下电时,必须严格遵循显示使能信号、驱动电源、显示时钟/ 数据信号、逻辑电源的时序。为满足下电时序要求,一般也是利用CPU的GPIO来控制。该设计利用D触发器及与门可实现DISP置低提前于驱动电压。采用DISP信号控制电源电路,当DISP置低时,HT66130/HT66137驱动芯片的驱动电源完全关掉,无须另外的GPIO口来控制。测试表明电路运行正常,能有效地控制上电、下电的时序,无乱码、锁存、残留显示等现象。而且在待命状态驱动电路功耗很小,仅为0.2 mW(包括电路与液晶显示器件)。