随着计算机和半导体技术的发展,使LED大屏幕显示系统成为集计算机控制、视频、光电子、微电子、通信、数字图像处理技术为一体的显示设备。随着大屏幕显示技术的发展进步,需要处理的数据大量增加,系统的频率更高、规模更大,对显示控制系统的要求也不断提高。目前LED显示器常采用8位/16位的微处理器,由于其运行速度、寻址能力和功耗等问题,已难满足显示区域较大、显示内容切换频繁的相对复杂的应用场合。存在系统体积较大、调试困难、不易修改、系统不稳定等诸多问题。ARM具有体积小、功耗低、数据处理能力强等特性。在无计算机支持的独立显示系统中,采用嵌入式系统来解决信息显示的诸多要求是一个理想的方案。因此本设计以LPC2210微处理器为控制电路核心,解决了系统的运行速度、寻址能力和功耗等问题,从而支持更大可视区域的稳定显示、存储更多的显示内容。

1 系统硬件组成及原理

本系统选用Philips公司生产的LPC2210微处理器,以功耗小、成本低的ARM7TDM I为内核系统的硬件构成。该系统主要由显示控制电路和LED显示屏部分构成,如图1所示。

以ARM7(LPC2210)微处理器为为核心的控制电路主要完成数据转换信号控制工作。LED显示屏的扫描驱动电路主要采用74HCl38和74HC595等来完成行扫描并以控制时序的方式来完成列控制。显示屏以LED为像素,由LED点阵显示单元拼接而成,本设计的显示屏为16行×64列的点阵结构。

在设计中,采用LPC2210P0口的16个引脚作为显示控制电路的接口,并分别对应屏的使能端EN、行选中信号端(A,B,C,D)、行点亮数据信号端(GD1,GD2,RD1,RD2)和2路时序信号LAT,CLK等。

2 系统软件设计

由于本LED显示屏的显示控制电路,主要采用74HCl38和74HC595完成行扫描,以控制时序的方式完成列控制,且这些时序是由软件部分完成的,因此在软件系统的设计中,首要考虑时序逻辑的合理设计与实现。在本LED显示屏中,需要2路时序分别是完成数据缓存的缓存时序CLK及将缓存数据点亮的点屏时序:LAT。CLK出现上升沿后,将数据依次存入屏的缓存,LAT出现上升沿后,屏将缓存内容送到屏的某一行。除此之外还要考虑行扫描过程中行的选择以及显示模块、通信模块、清屏模块等,子模块的编写与各子模块间的协调使用等问题。

需要指出的是为了提高LED显示屏的可扩展性,就势必使系统提高了对频率的要求,为此本设计在系统软件的设计过程中,利用LPC2210微处理器自带的锁相环(PLL),对系统进行了倍频设计,以提高系统的可扩展性。系统软件架构设计,如图2所示。

2.1 PLL模块

LPC2210的PLI接收的输入时钟频率范围是10~25 MHz,选用11.059 2 MHz作为系统的外部晶振频率,首先需要配置PLL,计算公式如式(1)所示。

其中,Fosc为晶振频率,Fcco为PLL电流控制振荡器的频率,cclk为PLL的输出频率即处理器的时钟频率,M与P分别为PLL的倍增器值与分频器值。

CCO频率可由式(2)得到。

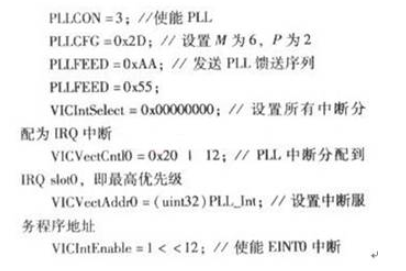

PLL模块部分源代码如下:

2.2 其它主要模块

主要完成行扫描及其该行每一个点的扫描模块

3 系统验证

使用ADSl.2进行在线仿真验证,通过对硬件的设计和对软件代码的编码与调试,实现了点阵LED屏以双色、多样化的方式显示各种信息的功能,同时可通过简单的级联来扩展显示屏。并分别在不调用与调用PLL模块的两种情下进行比较分析,得到了比较明显的现象,即在调用PLL模块的情况下系统显示更加稳定更加适合点阵LED屏的扩展。

4 结束语

本设计采用32位ARM嵌入式微处理器LPc2210,采用可扩展、模块化设计,以LED屏的显示电路和ARM微处理器控制电路为核心,实现点阵LED屏以双色、多样化的方式显示各种信息的功能,同时可通过简单的级联来扩展显示屏,解决了系统的运行速度、寻址能力和功耗等问题。