LDO也就是线性稳压电路,从应用的输入电压中减去超额的电压,产生经过调节的输出电压。LDO(低压降)稳压器通常使用功率晶体管(也称为传递设备)作为 PNP。本文将浅谈一下关于模拟电路应用之LDO的PSRR计算。

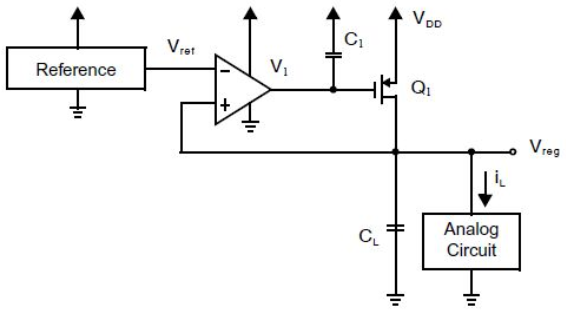

讲讲作者君最近有见过的一个很基本的电路:LDO(A low-dropout or LDO regulator is a DC linear voltage regulator that can regulate the output voltage even when the supply voltage is very close to the output voltage.),就是传说中的无处不在的稳压电路。

low-dropout or LDO regulator is a DC linear voltage regulator that can regulate the output voltage even when the supply voltage is very close to the output voltage.),就是传说中的无处不在的稳压电路。

作者君捣鼓这个电路的初衷,是看看我调整了input电压之后,PSRR有没有很显著的恶化。因为之前有个别人做好的LDO,但是input是bandgap的1.2V,作者君把input改成0.8V之后,就稍微改了一些东西:比如把之前OTA的input pair从pmos变成了nmos。然后,因为这个LDO的PSRR要求比较高,作者君就小小的捣鼓了一下PSRR的计算。

我们还是从书本来说起吧!

上面的图是来自“Analog Integrated Circuit Design, 2nd EdiTIon,Tony Chan Carusone, David Johns, Kenneth MarTIn”

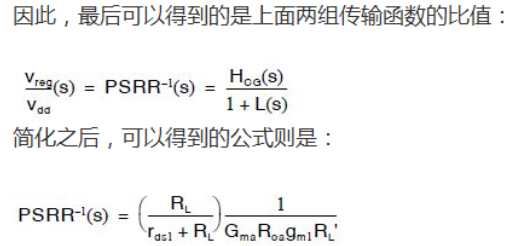

不管怎么说,我们要考虑一个系统的frequency response特性,首先跑不掉的就是loop gain。 因此,可以按照下面的公式算出loop gain,其中包括两个可以预计到的pole:一个在OTA的output,一个在LDO的output:

可以看出,DC时候的PSRR其实就是整个system的DC gain的一部分。因此,想得到一个大的PSRR,需要有一个比较大的gain的OTA,这个是可以预料到的。