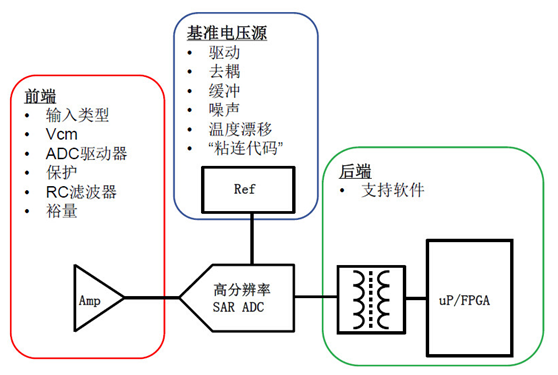

高精度逐次逼近型ADC支持电路的结构

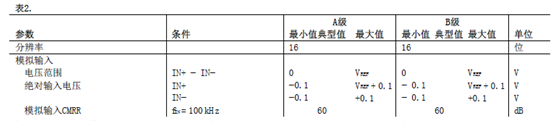

SAR基准电压源分为内部与外部

内部基准电压源

易于使用

节省空间

外部基准电

无与ADC集成的基准电压源

最佳性能(噪声、ppm/C漂移和初始精度)

可能获得更好的功效/多个ADC

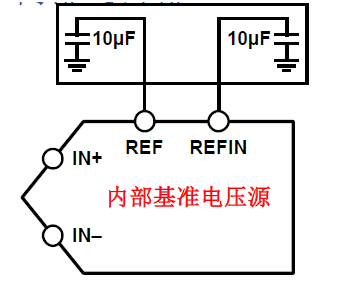

SAR基准电压输入

REF是开关电容输入

每一位电容ADC在位检验过程中均会切换至REF

电荷再分配会导致从REF吸取电荷

动态电流负载

吞吐速率的函数

内部位检验时钟的函数

MSB需要最大电荷

使用500欧姆电阻测得的电流

电流尖峰高达2.5mA

需要大储能电容,以获得稳定的基准电压

通常为10uF或以上

减少基准电压源驱动时的负担

基准电压源电路在转换之间为储能电容充电

ADC基准电流规定为特定吞吐速率时的平均电流

平均电流与吞吐速率成比例

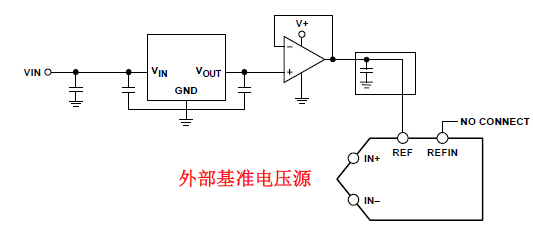

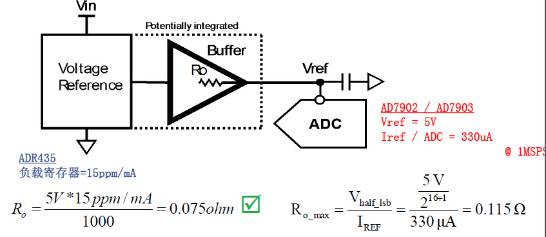

基准电压输出驱动

带隙基准电压源可以包含缓冲器(ADR43X、ADR45XX)

否则,可以使用合适的运放

电流负载应使基准电压下降小于0.5lsb

突发模式工作是最差的情况

基准电压源的输出电流大于总基准输入电流的平均值

基准电压源的吸电流能力

在故障条件下,ADC输入可能会超过基准电压

ADC驱动器从更宽电轨运行

电流/电荷释放到REF节点

基准电压源电路需要吸电流功能(ADR43X,ADR45XX)

放电超过REF电容上的电压

在故障过程中吸取ADC驱动器电流

老的基准电压源可能没有吸电流功能,仅有源电流功能

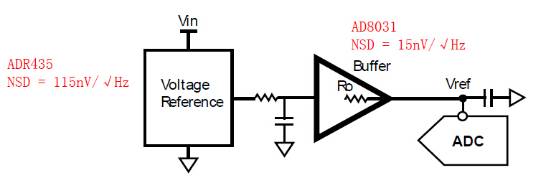

基准电压源缓冲器

当Ref驱动不足或uPower Ref时使用

用于驱动多个ADC

典型单位增益配置

低噪声

驱动大电容负载(10uF)

频率范围内的低输出阻抗

大储能电容可处理高频纹波

取决于吞吐速率

缓冲器可处理低频纹波

输入信号带宽

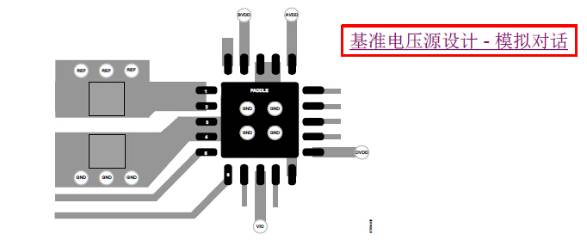

驱动多个ADC的基准电压缓冲器

每个电路板/系统一个基准电压源

同步采样型应用

每一个SAR ADC均具有其自己的储能电容

尽可能靠近REF引脚放置

星型连接至缓冲器,使串扰最小

缓冲器必须在大电容负载的情况下保持稳定

缓冲器必须具有充足的电流驱动能力

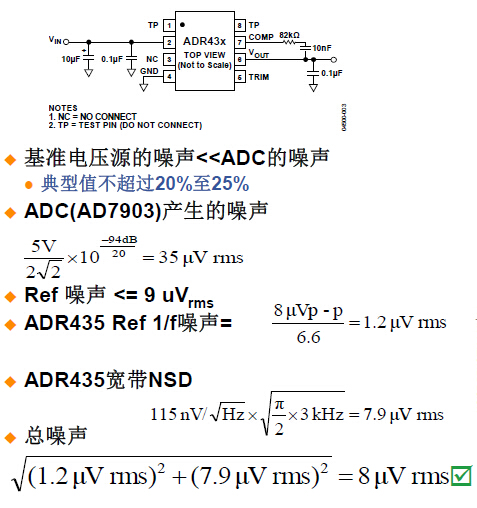

基准电压源补偿和噪声

缓冲器噪声

同样地,也可以估计缓冲器的噪声

需要估计在10uF负载(~16KHz)情况下的带宽

缓冲器噪声影响~2.4uV

基准电压源通常是主要噪声源

假设选择噪声相对较低的缓冲器

如果使用缓冲器,则可通过RC对基准电压噪声进行限带处理

可使用极低的截止频率(耦合100Hz)

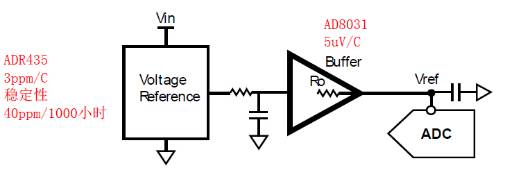

温度/时间漂移

以mV指定的基准电压源的初始精度

漂移极为重要的规格参数

多数系统常常校准

基准电压值中的漂移显示为ADC增益误差

多数良好的基准电压漂移《10ppm/C

ADR45XX系列漂移《2ppm/C

增加系统误差预算

基准问题–“粘连位”

设计不佳的基准电压电路显示为“粘连位”

由于噪声,SAR做出错误的位判断

相同的代码不断重复,而输入不断变化

低位中的所有零或所有

在接近满量程的输入端更重要

常见原因

储能电容的布局和大小

驱动强度不足/高输出阻抗

基准电压噪声/基准电压缓冲器太大

布局考量

储能电容布局至关重要

尽量靠近ADC基准引脚

使用宽走线连接

低阻抗接地路径或基准接地引脚(如有)

电容选择

低ESR

陶瓷X5R

越大越好,高达10uF,但取决于ADC电流要求。

模拟前端

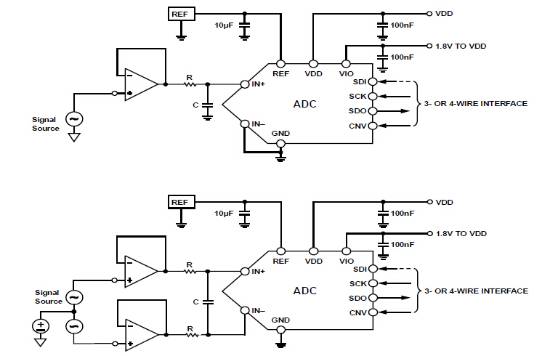

采样系统的典型前端连接

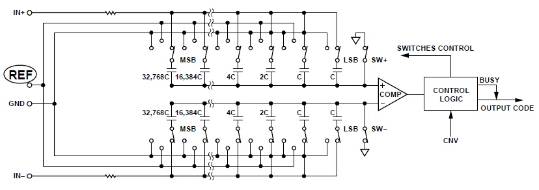

SAR ADC的模拟输入架构

选择某种输入类型的原因

各设计的优势和限制

遇到的常见错误

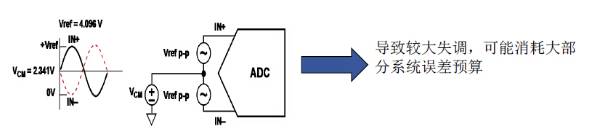

差分ADC的输入端没有反相信号

在伪差分ADC的IN-输入端施加非零直流电压

反相,但Vcm不正确

逐次逼近型器件的三种最常见的ADC输入结构类型 单端

简单是它的优点→?仅需要一条线即可将信号源的信号传递至ADC

信号以ADC的公共接地引脚为参考

对于许多应用,单端连接是可接受的完美解决方案

因此您为什么会想用其他的呢?。..。.

不能抑制信号链内的直流失调→?减小输入信号的动态范围

更易受到耦合噪声的影响

信号源和ADC应彼此靠近

如果检测信号地的需求增加,则可能会考虑伪差分器件

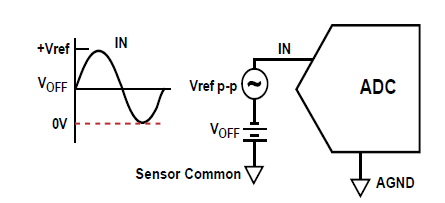

伪差分

将感知的信号地与ADC接地分开

IN-是信号源接地检测

ADC旨在抑制IN-上的干扰信号

伪差分器件可抑制哪种类型的干扰信号?

IN-允许输入的电压范围有限

较大的共模电压可能需考虑在输入端增加一个仪表放大器

SE器件的动态范围没有提高…如果需要更大的动态范围怎么办?

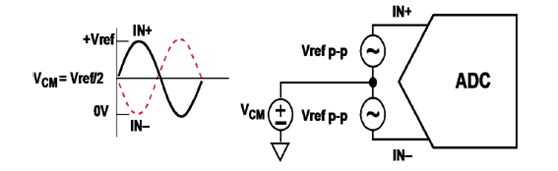

差分反相

提高动态范围?反相信号允许输入+/-满量程而非0至满量程…使动态范围加倍!!!

最大程度抑制噪声

往往消除偶阶失真产物

ADC旨在抑制输入干扰信号

和伪差分一样,架构限制可抑制的共用输入信号范围→?CMRR在此范围内非常好

信号必须为反相信号→?否则,很快违反共模限制

根据不同的架构,此器件可接受不同极性的电压输入

单极性→?通常具有0V至Vref或多倍Vref的绝对输入电压范围

双极性→?通常具有+/- Vref或多倍+/- Vref的绝对输入电压

对于任一极性信号均可采用上述所有ADC输入结构

选择正确的驱动放大器

选择正确的无源滤波器值

带宽/建立时间考虑因素

选择正确的放大器

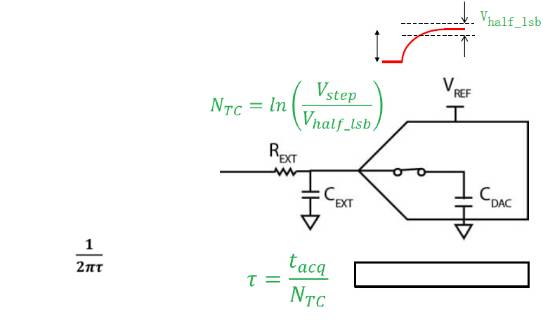

由于采用SAR ADC的开关电容架构,输入阻抗不会很高

很可能需要一个放大器,用于在输入信号源和ADC之间执行阻抗转换

根据采样速率、信号带宽和所使用的转换器,选择放大器对于实现所需的系统性能水平至关重要

计算RC滤波器带宽

R和C值考虑因素

CEXT衰减“反冲”,通常为两nF

太大导致驱动器不稳定

低电压系数NP0电容

REXT帮助放大器驱动CEXT

太小又会降低驱动器的相位裕量=》不稳定或振铃

太大导致失真增加。可能适用于较低的fin

放大器带宽应至少为2-3x RC带宽

SSBW用于低频(《100KHz)

LSBW用于多路复用/高频

对多路复用输入至关重要的建立时间(至0.001%)

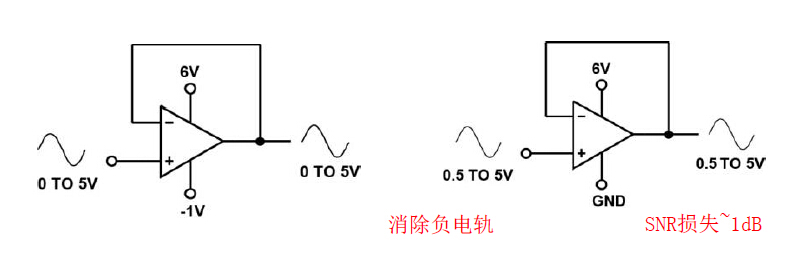

选择合适的放大器 - 裕量

失真性能需要上/下余量

对于R-R输出甚至可达1V或更多

可使用单极性电源,有损输入范围,SNR略有下降