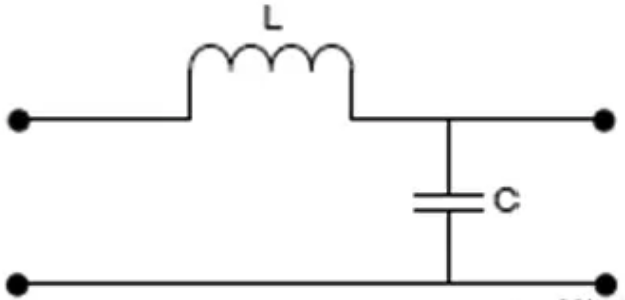

为了使USB3.0支援5Gbps的数据率,在旧的USB2.0数据对(D+和D-)基础上增加了两个差分数据对(超高速Tx及Rx)。此外,配合USB 3.0的芯片组以低至22nm的半导体工艺为基础。USB 3.0相对于 USB 2.0传输的频率升高,催生了在超高速线路上布设外部ESD保护元件时必须符合的严格阻抗匹配窗口。信号线路上增添任何少量的电容,都会改变阻抗,且因此降低数据传输的总体信号完整性。图1显示了无损耗传输线路的电路表征,其中额定阻抗表征为Z0。

Z0 = (L / C)1/2= 线路阻抗

图1 无损耗传输线路等效电路图

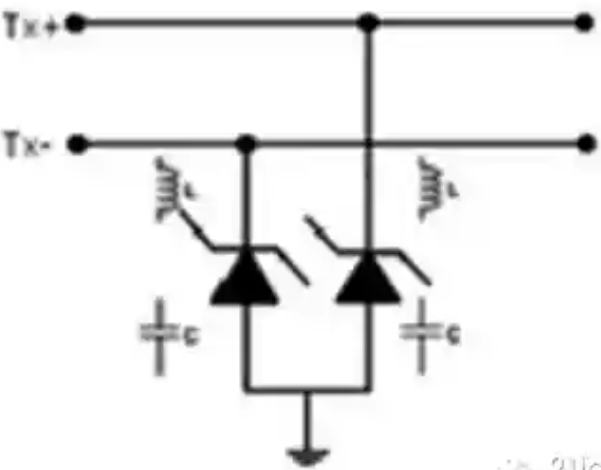

此传输线路模型能应用于几乎任何当今高速串联接口中存在的数据线路。此模型可以用于评估将ESD保护元件置于一条或多条数据线路上的效应。在最基本的形式下,可以看到用以保护的数据线路的齐纳二极管形式的ESD保护元件。此二极管有相应的结电容,以及源自封装内部接合线(bond wire)的少量串联电感,而此串联电感会变成数据线路的寄生元件,如图2所示。由于ESD保护元件中典型接合线的感抗通常不高于1nH,而且ESD保护元件的电容必须不高于1pF,对于2.5GHz USB 3.0信号而言,图2中电感的阻抗将低于电容的阻抗,在讨论中可以忽略此感抗。

图2 ESD保护元件寄生元件模型

随着数据线路上电压的变化,需要少量的电流来给寄生电容充电。在高频时,信号线路的电压迅速变化,此额外充电电流可能相当可观,因而降低了数据线路中流动的电流。此电流的降低导致数据线路阻抗轻微变化,影响它传输的功率总额。如果功率传输损耗过高,数据线路信号完整性就会出现下降。USB 3.0规格允许最大寄生电容为1.1pF(此值包含系统中在USB控制器外部的任何电容)。ESD保护元件的电容仅占系统外部电容中的一小部份。因此,当选择此类元件时,工程师应当始终谨记,保护元件的较低电容不仅维持数据线路的的信号完整性,还使下行系统中能够有更大的电容预算。