1 引言

采用光纤陀螺的捷联惯性导航系统是一种极具发展潜力的导航系统,对于其核心部件的光纤陀螺,尤其是中高精度光纤陀螺,环境温度带来的漂移是不容忽视的,因此对系统进行温度控制很有必要。温度控制电路是整个温控系统的硬件基础,其中涉及到温度采集,与微处理器通信,串口输出,控制数模转换芯片等多个组成部分。本文提出一种高效实用的FPGA 接口设计,它能够完成协调各个组成部分有序工作,准确、快速实现数据传输,严格控制信号时序等工作。

2 温控电路整体结构

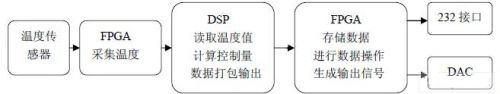

温控电路的整体结构框图如图1 所示。其中包括七路温度传感器,DSP, 232 接口芯片,DAC ,后端控制电路,上位机和FPGA 等多个组成部分。FPGA 接口是整个电路的核心。

图1 温控电路的整体结构框图

其中,温度传感器采用DALLAS 公司的DS18B20,它采用1-wire 总线协议,仅需1 根数据线进行通信。DSP 采用TI 公司的TMSVC33,它可以实现高速浮点运算。232 接口芯片采用MAXIM 公司的MAX3232,支持高达120kbps 的传输速率。DAC 采用TI 公司的TLV5620I,它是通过4 条串行信号控制的8 位4 路数模转换芯片。FPGA 选用ALTERA 公司的ACEX 系列的EP1K100,它时钟频率高,具有丰富内部资源,提供大量可编程IO 管脚,配置十分方便。基于FPGA 的温控电路接口在整个电路中具有非常重要的作用。FPGA 本身的高速并行结构为整个电路的性能提供了可靠保证。

3 温控电路工作流程

温控电路的工作流程如图2 所示。FPGA 与七路温度传感器通信,读取温度值,并存储于内部存储器中,每秒更新一次。FPGA 发送中断信号通知DSP 读取FPGA 中存储的温度值,DSP 根据当前温度值和控制算法计算出控制量。而后将温度值和控制量打包成一帧数据发送给FPGA。FPGA 将DSP 发送来的数据存储在内部存储器后,对数据进行操作,生成输出信号。

FPGA 一方面将数据串行发送给232 接口芯片,然后通过232 串口发送给上位机。上位机可通过监视软件实时观测温度值和控制量的变化情况,方便系统调试与*估;另一方面从数据中提取出控制量,将其串行输出到DAC,数字控制信号经过DA 转换后输出模拟控制电压到后端控制电路,实现对七路温度的闭环控制。

图2 温控电路的工作流程

4 FPGA 与外围电路之间的通信接口

FPGA 与外围电路之间的通信接口主要包括与温度传感器,DSP,232 接口芯片和DAC的通信接口四个部分。

(1) 与温度传感器的通信接口

本方案的温度传感器采用DS18B20,它通过硬件非常简单的1-wire 总线通信,由于硬件简单所以通信协议比较复杂。要实现与它的通信接口将占用大量FPGA 片内资源,而且本方案要进行七路温度采集,因此优化程序设计,减少冗余,节省资源显得尤为重要。

(2) 与DSP 的通信接口

DSP 与FPGA 的组合已经成为当今数字电路中非常流行的模式。FPGA 非常适合与DSP配合。本方案中,DSP 与FPGA 的通信接口主要由数据总线,地址总线和一些控制信号组成。FPGA 和DSP 之间由8 位数据总线连接,数据以字节形式并行传输。DSP 通过地址总线对FPGA的片内资源寻址。控制信号主要包括复位信号,中断信号和读写信号。

(3) 与232 接口芯片的通信接口

FPGA 与232 接口芯片的通信是通过收发两条数据线实现的。本方案中,只存在温控系统到上位机的单向数据传输,故仅需一条发送数据线就可以完成与232 接口芯片的通信。

(4) 与DAC 的通信接口

本方案选用TI 公司的TLV5620I 芯片作为DAC。它是8 位4 路电压数模转换器。对于它的数字控制基于由4 条信号线组成的串行总线。包括CLK,DATA,LOAD 和LDAC 四种信号。

5 FPGA 的逻辑设计

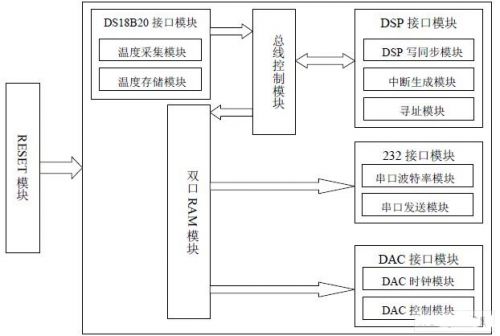

在温控电路的总体方案,硬件结构,工作流程和接口协议都确定后,就可以进行FPGA的逻辑设计了。FPGA 的逻辑设计是整个温控电路接口设计的重中之重。它基于verilog 硬件描述语言。良好的FPGA 逻辑设计应该是时序清晰,运行稳定,结果明确和节省资源的。它能够保证整个系统的可靠,稳定和高效。FPGA 的逻辑模块图如图3 所示。FPGA 内部逻辑大致分为RESET 模块,DS18B20 接口模块,总线控制模块,DSP 接口模块,双口RAM 模块,232 接口模块和DAC 接口模块等几部分。

图3 FPGA 的逻辑模块图

(1)RESET 模块

该模块生成全局复位信号。是所有模块中优先级最高的。系统上电后,该模块将复位信号拉低并持续1 秒而后拉高,对DSP 和FPGA 内部其他模块进行复位。

(2)DS18B20 接口模块

该模块用于实现与DS18B20 通信,读取并存储温度值。它包含2 个子模块。

一、温度采集模块

该模块实现与DS18B20 的通信协议。首先通过一个初始化序列对DS18B20 进行初始化,包括一个由主机发出的复位脉冲和其后由从机发出的存在脉冲。探测到存在脉冲之后,代表初始化完成,模块将发送ROM 操作命令。本方案中,执行SKIP ROM 跳过ROM 匹配。之后将发送存储器操作命令。温度转化和读取温度就在这部分完成。其中每一次读写操作都需要严格按照DS18B20 的读写时隙进行。该模块复杂程度高和占用资源多,是整个FPGA 中的重要模块。本方案一共有七路温度采集模块,它们的并行结构使得系统可以方便地实现对七路温度的实时监控。

二、温度存储模块

该模块的主要构成部分是一个14*8 位存储器,用于存储七路温度数值,每一路数值需要2 个8 位寄存器存放。存储完毕后,等待DSP 读取。

(3)DSP 接口模块

该模块主要用于与DSP 进行通信。它包含3 个子模块。

一、DSP 写信号同步模块

DSP 的数据写入在写信号控制下完成。由于DSP 和FPGA 采用不同的时钟源,所以DSP产生的写信号无法和FPGA 的主时钟同步。这样就会导致写数据错误。该模块用于将DSP 写信号与FPGA 的主时钟同步。

二、中断生成模块

由于本方案中,温度值每秒更新一次。在温度值更新后,通过中断信号通知DSP 读取温度值。该模块用于生成周期为1 秒的中断脉冲。

三、寻址模块

该模块对FPGA 片内资源进行编址,由DSP 的地址总线控制寻址。准确读写所需的数据。

(4)总线控制模块

DSP 和FPGA 之间的数据总线是双向总线,总线控制模块用于控制总线的数据流向。当DSP 从FPGA 中读取温度值时,总线控制模块将温度存储模块和数据总线相连,输出数据。当DSP 向FPGA 中写数据时,总线控制模块将数据总线和双口RAM 模块相连,输入数据。

(5)双口RAM 模块

该模块主要实现以下三个功能:当DSP 写数据时,将数据存储于内部存储器中;当数据存储完毕后,将其中的控制量发送给DAC 控制模块;与串口发送模块通信,将所有数据依次串行输出。

(6) 232 接口模块

该模块用于实现串口数据输出,它包含2 个子模块:

一、串口波特率模块

串口通信协议要求数据收发双方有相同的波特率。该模块用于设定串口通信波特率。

二、串口发送模块

双口RAM 模块将数据存储完毕后,将给串口发送模块一个标志信号。串口发送模块接到此信号后,依次将双口RAM 模块中存储的数据串行输出。

(7)DAC 接口模块

该模块包含2 个子模块:

一、DAC 时钟模块

DAC 需要特定频率范围的时钟来驱动。该模块用于生成驱动DAC 的时钟信号。

二、DAC 控制模块

该模块用于生成DAC 控制信号。它的基本原理是将双口RAM 模块输出的7 路控制量存储在内部存储器,然后根据DAC 的接口协议生成CLK,DATA,LOAD 和LDAC 等控制信号,这些信号将驱动DAC 的工作,将数字控制量转换成模拟电压值。

图4 温度控制电路

6 结束语

经过验证,接口满足系统要求,工作状态良好。本文所述的FPGA 接口设计方案是可靠,稳定和高效的。可为其他相关应用提供有益的借鉴。