MIL-STD-1553B是一种时分制,命令/响应,集中控制式多路传输的半双工串行数据总线,其传输速度为1Mb/s,字长为20b,数据有效长度为16b,信息量最大的长度为32个字。其信息格式有总线控制器BC(Bus Controller)到远程终端RT(Remote Terminal),RT到RC,RT到RT,广播式和系统控制式。

MIL-STD-1553B总线协议已经发展成为国际公认的数据总线标准,广泛地应用于航空电子综合系统中,目前国内外开发的各种1553B总线采集卡,大多采用的是美国DDC公司生产的BU-6150接口芯片,但是该芯片价格比较昂贵,开发成本较高,另许多商家望而兴叹。本文介绍的基于DSP的1553B总线通讯模块的设计,采用TI公司TMS320F206DSP芯片进行数字信号处理,用FPGA进行现场反复编程,降低了设计成本,满足了1553B通讯模块的开发需求。

1 TMS320F206的简介

该1553B总线通讯模块的DSP采用TI公司的TMS320F206,用来实现1553B总线协议的主体部分,实现字和消息的处理等功能,TMS320F206是TI公司近年来推出的一种性价比较高的定点DSP芯片,采用静态CMOS集成电路工艺制造而成,DSP芯片先进的哈佛结构允许程序存储器和数据存储器独立编址、独立访问,两条总线可允许数据与指令的读取同时进行,从而使数据的吞吐率提高了一倍;专用的指令集提供了功能强大的信号处理操作。TMS320F206主要特点如下:

(1)5V工作电压,20MHz主频时,指令周期50ns;3个外部引脚中断;8级内部硬件堆栈,存放调用/中断返回地址;硬件等待;休眠的IDLE模式,低功耗;标准的IEEE1149.1仿真口。

(2)片内64k程序空间,64k数据空间,64kI/O空间,32k全局存储空间,片内544×16b双寻址RAM,32k×16b用户可编程FLASH,作为程序空间,4k×16b单寻址RAM,程序空间和数据空间之前可以进行数据搬移。

(3)片内16b定时器,片上软等待产生器,可以分别为程序空间,数据空间,I/O空间产生0-7个等待,片上振荡器和锁相环有倍频和分频功能,32b算术逻辑单元/累加器,16×16b乘法器,全双工异步串口UART,增强的同步串口,带4级FIFO。

2 系统的组成框图和工作原理

检测仪采用单片机技术,可编程逻辑器件(FPGA)技术,数字信号处理(DSP)技术,结合1553B总线收发技术研制而成。既可以对单个航空电子设备进行离线检测,也可对飞机的整个总线的运行和各个记载设备的数据传输进行在线检测。检测仪整体采用个人数字助理(PDA)技术,数据输入、输出、处理、控制、显示等均集中在检测仪。

系统组成框图如图1所示。

从数据信号流程方面:收数据时,外部数据送到收发器进行电压转换后,成为一组20b的串行数据,经过FPGA芯片EP20K200处理成16b并行数据经扩展口送到DSP处理,然后经双口RAM进行数据缓存,需要显示数据时,单片机CPU对双口RAM送来的16b并行数据进行分析存储,按要求转换成十六进制,二进制或者工程单位制送显示器显示,发数据时,CPU将键盘输入的数据按照十六进制、二进制或者工程单位制经转换后送双口RAM缓存,DSP从双口RAM读入数据,预处理后送EP20K200,EP20K200再进行转换处理,输出一组20b的串行数据到收发器,经变压耦合成符合1553B标准要求的串行数据,再经收发接口发送到数据总线上。

3 硬件电路设计

3.1 接收器和发送器

1553B航空电子系统中,各终端设备与总线之间采用的是耦合的方式,分为变压器耦合和直接耦合,采用的美国DDC公司的BU-63152芯片,具有两个完全独立的双余度端口,完全满足1553B总线收、发的要求,接收器操作模式下,在引脚STROMB控制下,数据被变成双向的TTL电平,从RX DATA OUT和其非脚输出到下一级译码电路,发送器操作模式下,在引脚INHIBIT控制下,发送器部分从编码电路接收数据,发送到数据总线上。

3.2 FPGA模块

将FPGA技术与数字信号处理DSP技术相结合是现代电子设计中常用的方法,该模块中的FPGA芯片接口主要实现以下功能:

(1)将总线上的串行信息流转换成处理机可以处理的并行信息或者与之相反;

(2)接收或发送信息时,能够识别或生成标准的1553B信息字和消息。

(3)完成与处理机之间的信息交换,包括1553B信息地址的分配,命令字(或状态字)的译码或返回状态字、发送数据字等。

用FPGA实现编解码器,其基本功能与前面提到的BU-61580芯片相似,是该1553B总线检测仪的关键技术。

3.3 DSP模块

TMS320F206是TI公司近年推出的一款设计成本最低,结构功能复杂度也较低的定点DSP,片内32k FLASH,4.5k RAM可以满足处理规模适中的任务,该检测仪中DSP模块的设计主要是对时钟电路,中断以及数据和地址总线的接口技术的把握,其主要接口电路如图2所示。

由DSP接口电路图可以看出,DSP模块为整个系统提供了时钟电路,DSP芯片的中断由EP20K200产生,一方面通知F206读取数据,一方面通知DSP进行错误处理,由于DSP芯片的流水线操作方式,数字信号处理速度功能强大,满足了1553B协议传输速率大的特点。

3.4 双口RAM和显示模块

由于在高速数据处理和采集系统中容易造成数据堵塞现象,高速数据接口的设计对整个系统数据传输的畅通起着重要的作用,该设计中采用的美国DDC公司的8k双口静态RAM IDT7025解决了数据堵塞的问题。

在该设计中显示模块采用了一种内存接显示模块的硬件连接方式。DSP将欲显示的数据送入双口RAM,51单片机不断扫描内存,根据内存中的数据做出相应的处理,不断刷新显示屏上的内容,双口RAM的BUSY信号线为避免左右端口同时对同一存储单元写操作提供了硬件支持。设计中液晶显示模块采用16×16点阵的中文显示模块。

4 系统软件设计

该1553B航空电子总线检测仪软件设计主要包括3大部分,用以驱动数据采集板卡,完成对各寄存器的配置,实现数据的收发检测。

4.1 FPGA控制程序

该部分采用硬件描述语言VHDL进行编程,用Synplify进行综合,以及采用Max+Plus II进行时序仿真,在FPGA上实现的MIL-STD-1553B总线接口中的曼彻斯特码编码、解码器,该逻辑可由状态机实现,可划分为4个状态进行;第1个状态行是空闲状态,当检测到数据跳变沿时,进入第2个状态;第2个状态为有效同步字头检测状态;当检测到有效同步字头时,启动第3个状态,用锁相环分离时钟,进行码型转换;当数据有效时进入第4个状态,进行并/串转换及奇偶校验。FPGA接收数据流程如图3所示。

4.2 DSP模块控制程序

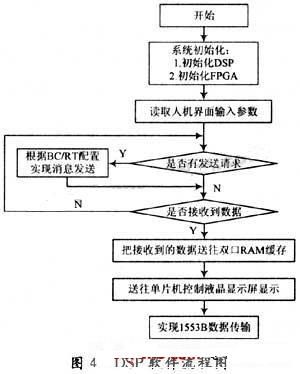

DSP部分的软件采用C语言和汇编语言混合编程,即具有C语言可移植性强的特点,又具有汇编语言执行速率快和直观的特点,该设计中DSP软件设计主要完成对FPGA和其内部通讯寄存器初始化;向FPGA发送数据时的控制命令操作,接受数据时命令字,状态字的处理,以及通知FPGA接受数据等,是整个系统控制的核心部分。图4给出DSP软件控制流程图。

5 结语

基于1553B总线的航空电子检测仪主要用于部队航空电子设备在线和离线检测,同时满足BC和RT的功能,PDA的设计对检测也提供了极大便利,当然由于设计处于样机阶段,还存在一些不完善的地方,今后的改进空间还比较大。