空时编码(Space—Time Block Coding,STBC)是达到或接近MIMO无线信道容量的一种有效的编码方式。空时编码方式的盲识别是通信对抗领域需迫切研究的领域,其能够为MIMO系统对抗技术提供基础和技术支撑,具有重要的研究价值。

时滞相关算法是根据不同空时编码的相关矩阵在不同时延统计下的差异性,采用逐级对比,实现对空时编码方式的盲识别。拥有计算精度高,抗频偏效果好等优点。文中提出一种基于ADI公司DSP芯片TigerSHARCTS201S的空时编码盲识别方案设计和实现。

1系统硬件设计

1.1系统硬件框图

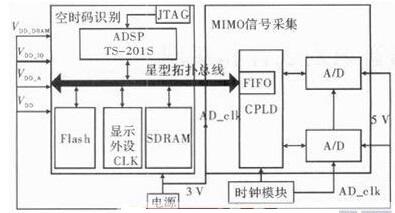

系统硬件框图如图1所示。由信号处理、信号采集、电源、时钟4部分构成,信号采集由CPLD和ADC组成,负责完成A/D转换,信号处理由TS201S芯片及其外设组成,用于存储A/D采样的数据,并进行空时码盲识别运算处理。电源模块为其他所有模块提供正常工作所需的电压,时钟模块中由晶振和倍频芯片组成,提供系统所需时钟。

图1 系统硬件框图

系统工作时,设备首先通电初始化,从Flash中载入用户应用程序,继而通过CPLD控制ADC进行数据采集,并利用DMA中断方式读取数据并进行编码识别运算。

1.2 TigerSHARC TS201S简介

TigerSHARC TS201S兼有ASIC和FPGA的信号处理性能和指令集处理器的高度可编程性与灵活性,适用于高性能、大存储量的信号处理与图像应用。

TS201S内部分为DSP核和I/O接口两部分,通过4条总线传输数据、地址和控制信息。并提供完全可中断的编程模式,支持汇编和C/C++语言编程,32/40位的浮点运算及最高64位的定点运算。在600 MHz时钟速率下,可达到每秒48亿次乘加运算。

1.3电源、时钟和总线方案设计

TS201S和AD7864对电源的要求较高,以TS201S内核时钟500 MHz为例,4个电源VDD、VDD_A、VDD_IO、VDD_DRAM的精度要求控制在5%以内。因此系统中的电源芯片采用了,其精度可达1%.

时钟模块中,晶振产生27 MHz时钟通过倍频芯片得到54 MHz时钟后进入CPLD,一方面作为TS201S的系统时钟SCLK,另一方面在CPLD内12分频后作为AD7864的工作时钟信号AD_CLK.为防止其对系统电源产生耦合干扰,晶振和倍频芯片的电源与本板电源之间要用电感或磁珠进行隔离。

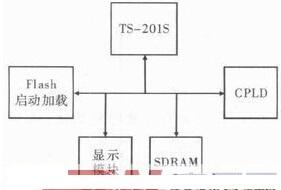

在系统总线负载较重的情况下,设计不当会限制总线只能在低频下工作甚至无法读取数据。由于环形结构上任一负载的变化均会影响到其他负载的工作,设计中采用了星形总线结构,如图2所示。

图2 星形总线结构

1.4信号采集方案设计

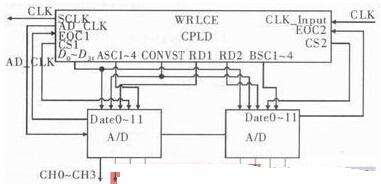

信号采集模块由CPLD和两片ADC组成,A/D转换芯片采用AD公司生产的AD7864,其转换精度12位,最高吞吐量520 ksample.s-1,转换时间最快为1.65μs,采样保持0.35μs,此外其单电源和低功耗特性最低可达20 Uw,其能够满足系统的要求,简化硬件设计。

信号采集前,需对AD7864的一些输入引脚进行配置,南Alterta公司的CPLD产品MAX3256完成。如图3所示,CONVST为使能输入引脚,置位高可控制AD7864启动。CS为片选信号,低电平有效。RD为读使能,低电平有效,当CS有效且RD为低,才允许AD7864输出转换结果,此时WR必须为高。引脚SL1~SL4是AD7864的通道选择输入引脚,高电平有效。H/S SEL为高时表示将通过软件方式来选择A/D转换通道,反之表示硬件选择。当转换结束后,EOC引脚输入低电平。

图3 信号采集

AD7864采用分时输出方式,采样信号来自TS201S的定时/计数器,每次计数器满时TMROE引脚会产生4个总线时钟的高电平,CPLD中对此信号做反向后作为AD7864的CONVST信号,在数据传输中,片1占低位数据线,片2占高位数据线,分时可防止总线冲突。

1.5显示方案设计

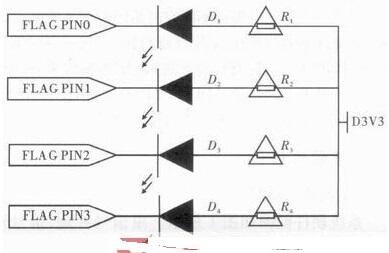

系统采用FLAG PIN外接LED做为进度显示,DSP在执行到不同的处理进度时通过改变FLAG PIN口的电平控制对应的LED导通,以指示当前数据分析的步骤。图4为外接LED的连接图,每个FLAG PIN上的LED均不影响其他FLAG PIN接口,在LED后使用了一个上拉电阻接VCC.

图4 为外接LED的连接图

系统复位时,所有FLAG PIN置高电平,ADC采集完毕触发DMA中断,从SDRAM中读取数据,并进入到预白化处理,此时FLAG PIN1至低电平,依据算法,对白化后的数据进行时滞相关分析,并利用码字表判决响应码型时,并分别拉低FLAG PIN2和FLAG PIN3.

该种方法配置灵活、软件简单,系统采用4个FLAGPIN来布置显示,DSP拥有足够的IO接口使用,在设计时充分利用了硬件资源,同时利用DMA中断,有效提高了CPU的效率,也实现了资源的共享和并行处理,同时还在芯片运算过程中及时发现故障并定位处理。

2系统软件设计

2.1空时编码盲识别原理

STBC通过在时间与空间进行联合编码达到提高系统传输性能的目的,因此在不同时刻从不同天线发送的数据具有一定的相关性,而不同空时编码之间的相关度并不同,因此可利用该相关度来区分不同的码型,从而将空时编码的模式识别出来。

2.2空时编码盲识别方法

(1)预白化。预白化的目的是去除信道对接收信号相关性的影响。白化矩阵W通过对分时相关矩阵P做特征值分解得到

![]()

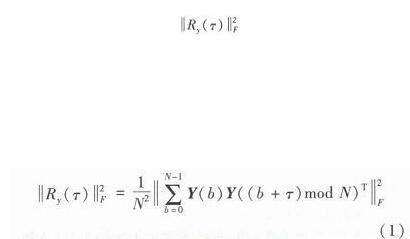

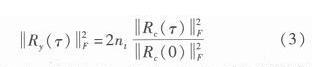

,其中A-1为特征值矩阵Λ的广义逆。W与原数据相乘便可得到解相关矩阵Y.(2)计算时滞相关度。利用接收信号预白化后得到的解相关矩阵Y,依据统计学公式计算时滞相关范数

空时编码矩阵的理论时滞相关特性仅与编码矩阵本身有关。因此,应用与式(1)相同的形式,可将编码矩阵不同的列进行矩阵乘加运算,并取F范数来表征。

由此得出计算空时编码的时滞相关矩阵R(τ)

其中,空时编码矩阵的每一列代表不同的发射时刻,A(u)是码型A编码矩阵的第u列,l为码型分组长度。已预白化后的接收信号矩阵与发送端编码矩阵,在时滞相关函数F范数上有如下关系

(3)判决码型。遍历候选码集,计算出接收信号与候选码集中每一种空时码的相关度,取其中最相关的码型便为判决码型。

2.3软件设计

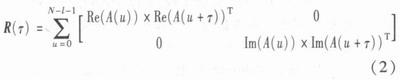

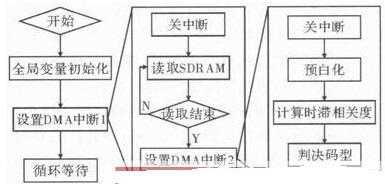

软件系统采用模块化结构软件系统采用模块化结构设计,程序流程如图5所示。包括系统启动、配置系统寄存器、设置全局变量和开启中断控制等。当ADC模块将采样数据全部写入SDRAM后,CPLD通知DSP触发DMA中断1,将SDRAM中的数据读入DSP,读取结束后DMA触发中断2,并对ADC采样数据进行处理:(1)预白化,去除新到对采样数据相关性的影响。(2)计算采样数据与候选集中每种码字的时滞相关度。(3)根据上述计算结果,选取使时滞相关度最小的码型为判决码型。

图5 软件系统采用模块化结构

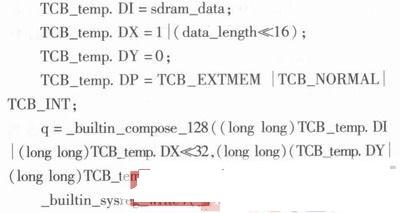

通过对DMAC寄存器的设置,可控制DMA的流向、通道和方式,典型的数据读取关键代码如下:

数据处理部分的关键函数包括白化和时滞相关量计算,数据传递采用了单维读入与多维传递的方式,即将多天线的数据按照天线顺序依次读入,但在DSP内部数据传递时,多根天线的数据按照时间顺序传递,在函数内部手动寻址,即符合算法要求,又加快了数据处理的速度。数据处理时包括大量的矩阵转置和乘加操作,在计算时优化为内积计算模式,使用ALU运算块X和Y,每个周期并行计算时滞矩阵两列之间的相关范数,这便节省了内存资源,减少了寻址次数,且加快了计算速度。

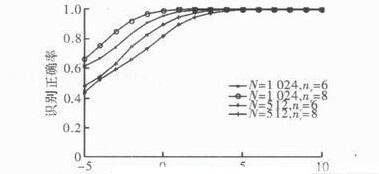

本算法在不同参数下的Matlab性能仿真如图6所示,采样数据越长,接收天线数越多,识别性能也越好。实际测试证明与期望相一致,验证了设计的合理性和正确性。

图6 算法在不同参数下的Matlab性能仿真

3结束语

DSP芯片具有的特殊软硬件结构和指令系统,使其能高速处理各种数字信号处理算法。基于此设计的空时编码盲识别方法具有速度快、精度高的特点。同时该系统依靠简洁的外部硬件电路设计和合理的软件程序设计,能够实现对常用空时编码模式的正确识别。且该系统的可扩展性良好,当需要识别最新的空时编码时,只需将其放入编码方式候选集中,为其分配显示接口即可,而无需过多更改硬件设置及软件程序。