1误码测试系统概述

Cygnal公司的单片机C8051F005具有高速8051微控制器内核,速度可达25MIPS,指令为流水线指令结构,70%的指令的执行时间为1个或2个系统时钟周期;可片内JTAG调试和边界扫描,这样可提供全速、非侵人式的在系统调试(不需仿真器);片内有多达60KB的FlashROM和2KB RAM,用户无需再外扩存储器;可同时使用的硬件SMBus(I2C兼容)、SPI及UART串口,4个通用16位计数器/定时器。

VSC8228可提供的一个双通道重发器或重定时器,能应用于光纤信道、千比特以太网、SONET/SDH以及无限带宽等多种领域。设备支持速率从125Mbps~4.25Gbps。该芯片可以将输入的串行数据在重定时器模式下与本地的参考时钟同步,内置的码型产生器与检测器可以产生与探测27、223、231的伪随机码,40或64位用户定义码型以及光纤信号CRPAT、CJTPAT、CSPAT码型。它含128个寄存器,可通过SPI或者I2C串行总线设置相关寄存器,可以实现误码检测功能。

误码测试系统可分为两个部分:误码测试部分和人机界面。测试部分由VSC8228芯片来实现。它完成伪随机码型的产生、同步及对比检测,计算出误码个数。人机界面子系统在整个测试系统中作为系统控制核心单元,通过人机界面完成系统作业。以C8051F005单片机作为人机界面硬件的控制部分,对VSC8228芯片的控制、误码率的计算以及测试子系统的各状态的显示都通过PC机的界面来实现。PC界面采用Delphi语言编写。

误码测试仪的工作流程如下:PC界面通过RS232串口实现与C8051F005的通信,将对VSC8228各寄存器的没置发送给C8051F005单片机,每个控制命令为16位;单片机通过SPI口将上位机发送过来的控制命令转发给VSC8228,完成VSC8228各寄存器的设置。为了实时地显示误码测试仪的工作状态,单片机每秒扫描一次各寄存器,将其值通过RS232串口上传到PC界面。

由此可见,C8051F005单片机起着VSC8228与上位机通信的桥梁作用,它与上位机的串口通信以及与VSC8228的SPI通信在误码测试仪的实现过程中起着十分重要的作用。下面通过软硬件设计详细分析这两种通信。

2 误码测试系统的实现

2.1 硬件设计

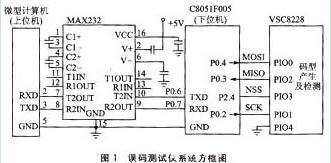

利用C8051F005单片机的串行接口,通过RS232异步通信接口与上位机进行通信。C8051F005通过串行口直接接收PC上位传送来的串行数据,然后把接收的数据存入数据存储器;同样,C8051F005通过串行口直接把数据传送给PC机。系统结构框图如图1所示。

C8051F005有一个特别的交叉开关,可将数字I/O资源分配到物理I/O端口引脚。C8051F005通过设置交叉开关来同时使用SMBus(I2C兼容)、SPI及UART串口等。VSC8228也可通过SPI或者I2C串行总线设置相关寄存器,但由于SPI通信的速率比I2C通信快,因此为了实现误码的高速测试,这里选择SPI作为C8051F005与VSC8228的通信协议。

SPI接口协议要求接口设备按主从方式进行配置,且同一时间内总线上只能有一个主器件。一般情况下,实现SPI接口需要3或4根线。其中:主出从入(MOSI)信号是主器件的输出和从器件的输入,数据传输时最高位在先;主人从出(MISO)信号是从器件的输出和主器件的输入,数据传输时也是最高位在先。当SPI从器件未被选中时,它将MISO引脚置于高阻状态。串行时钟(SCK)信号是用于同步主器件和从器件之间在MOSI和MISO线上的串行数据传输。从选择(NSS)信号是一个输入信号,主器件用它来选择处于从方式的SPI模块,在主方式时用于禁止SPI模块。当处于从方式时,它被拉为低电平以启动一次数据传输,并在传输期间保持低电平。

误码测试系统中,以C8051F005作为主器件,VSC8228为从器件,由于NSS为从器件选择使用,将单片机的NSS引脚(P0.5)置高,用P2.4引脚与VSC8228的NSS引脚(PIO3)相连。根据MOSI及MISO上的数据在SCK的哪种极性和相位上有效,单片机上的SPI通信有四种工作模式;但是VSC8228的SPl只有一种工作模式,故在对单片机的SPI控制器进行设置时必须考虑这点。图2是VSC8228的SPI通信时序。在SPI通信时,先传输7位地址,后传输读写控制位OP(OP为0时表示读,OP为1时表示写),最后传输8位数据,故SPI通信的命令字长度为16位。

2.2 下位机软件设计

下位机采用中断方式实现与上位机的通信,单片机用SPI与VSC8228误码测试模块的通信。每当串行口接收或发送完一组串行数据时,就产生一个中断请求。串行中断请求在单片机芯片内部自动由硬件置位发生,具有实时性高的特点。图3是单片机的控制程序流程。

对单片机进行程序初始化,包括看门狗、系统时钟、I/O口、SPI寄存器、UART口等。C8051F005单片机具有看门狗,但是看门狗到一定时间,将重启单片机,为防止这种现象的产生,初始化里禁止了看门狗。SPI的初始化主要是对启动SPI的相关控制寄存器进行配置。UART的初始化主要是对串口的控制字进行设置。I/O口的初始化通过设置交叉开关来启动SPI与UART口,并将有关输出设置为推挽输出。

系统时钟初始化模块,由于是选择外部晶振作为时钟源,根据C8051F005的要求,在通过外部振荡器控制寄存器OSCXCN选择了外部晶振后,需等待至少1ms后再查询等待OSCXCN寄存器中的D7位,即XTLVLD位变为1,表明外部晶振正在运行并已工作稳定,然后才能通过内部振荡器控制寄存器OSCICN的D3位,即CLKSL置1来选择外部晶振。

C8051F005使用4个特殊功能寄存器来实现对SPI的控制和访问。这4个寄存器分别是控制寄存器(SPI0CN)、数据寄存器(SPI0DAT)、配置寄存器(SPIOCFG)和时钟频率寄存器(SPI0CKR)。当以C8051F005为主器件时,应将主允许标志(MSTEN,SPI0CN.1)置1,同时将SPI使能SPIEN(SPI0CN.0)置1。通过CKPHA(SPI0CFG.7)和CKPOL(SPI0CFG.6)可选择SPI相位与极性,从而实现SPI通信的四种模式,但因为VSC8228只支持一种方式,所以将它们同时置为0,则空闲时SCK为低,此时的系统将在上升沿发送数据,下降沿接收数据(时序图见图2)。由于在MCU中,SCK的频率可从系统时钟分频得到,因此该频率可由下式给出:

其中fsysclk是系统时钟频率,SPI0CKR是SPI0CKR寄存器中的8位值。

为了防止上次测试对本次的影响,在程序的初始化之后,对VSC8228写入重肩命令,这样每次运行程序都将VSC8228的寄存器恢复为默认值。界面发送的数据为16位,其中8位地址,8位数据,而且每个数据是一个字符。为让单片机识别控制命令已发完,最后一个16位数据设为FFFF。另外,每16位数据之间加入了100 ms的延时,这样Spcomm控件就会把每16位数据当成1帧,单片机也能够正确地接收所有数据。

单片机用中断的方法来接收界面传过来的数据。每接到一个数据,即一个字符,就执行中断子程序,将接收到的数据的最低位存人数组。串口中断子程序流程如图4所示。当接收到16个,就接收完1帧,转入执行主程序去对收到的16位进行处理。处理过程就是将收到的16个数据(存放在数组中),通过移位跟“或”运算,综合成16位的数据。然后,通过移位运算,取高8位作为地址,低8位作为数据。对于接收的16位数据,如果不是FFFF,则将提取出来的8位数据,发送给提取出来的8位地址对应的寄存器;如果接收的16位数据为FFFF,表示所有的控制命令已经发完,这时VSC8228的全部寄存器设置完毕,VSC8228的码型产生模块以及检测模块开始工作。此时,单片机每秒扫描一次所有寄存器的值,并将其值通过串口传给界面,界面对串口传送过来的数据进行处理。

本设计中,SPI的数据传输过程如下:

① 关闭中断允许。

② MCU将VSC8228的NSS拉低(即置P2.4=0),以选中从器件VSC8228。

③ 将待发送的数据写入数据寄存器(SPI0DAT),即写发送缓冲器。如果SPI移位寄存器为空,发送缓冲器中的数据字节被传送到移位寄存器,数据传输开始。

④ 在SCK上提供串行时钟,同时在MOSI线上串行移出数据。传输结束后,SPIF(SPI0CN.7)标志被置1。

⑤ 传输结束,将NSS拉高,打开中断允许。

以下是SPI写VSC8228测试程序的关键代码:

2.3 上位机软件设计

上位机主要实现以下功能:显示当前日期和时间;根据检测需要设置检测参数(产生码型、检测码型、速率、输出去重、摆动输入均衡、探测门限等);运行时间及BER的计算,控制按钮及LED显示检测状态。状态灯可以显示的状态有“无信号”、“同步态”、“失同步态”与“等待态”等。它是在WindowsXP环境下采用Delphi语言编写的。首先在Delphi里加载串行通信功能的SPCOMM控件,它使用非常方便。由于Delphi采用事件驱动模式,程序员只需要对Delphi组件的属性、事件进行编程,然后再由这些组件对相应的事件进行响应。这样就使得各个事件彼此完全独立,减少事件间的耦合性,可以大大提高程序的稳定性和可靠性,同时简化程序的编码过程。

SPCOMM应用的核心在于主线程、读线程和写线程之间的消息传递机制,而通信数据相关信息的传递也是以消息传递的方式进行的。在使用SPCOMM进行串口通信编程时,需特别注意以下两个问题:首先,SPCOMM是通过ReadIntervalTimeout属性的设置来确定所接收到的数据是否属于同一帧数据的,其默认值是100 ms。也就是说,只要任何两个字节到达的时间间隔小于100 ms,都被认为是属于同一帧数据。另外,SPCOMM的默认属性设置是支持软件流控制的,用于流控制的字符是13H(XoffChar)和11H(XonChar),当单片机以二进制方式发送数据时,必须禁用SPCOMM对于软件流控制的支持,即Inx_XonXoff-Flow属性设为False,否则,在数据帧中出现的13H、11H会被SPCOMM作为控制字符而加以忽略。

由于单片机的SPI口对VSC8228进行控制时须向每个寄存器发控制字,所以界面就要求发送1个地址加1个字节数据的形式,这样就有16位;同时为单片机能够方便地分清每个帧(1字节地址加1字节数据),每次发送1帧就延时100 ms。单片机每秒扫描1次VSC8228的全部寄存器,并将数据传送给界面,因此,界面首先要一帧一帧地识别出来,然后对于某些地址的数据进行特定的操作。

误码率是误码个数与码总个数的比值。码总个数是检测时间和速率的乘积。对不同的速率有不同的总数。由此,得出误码率。

关键代码如下:

3 误码测试性能

本设计经实验测试,上位机与下位机的串口通信以及MCU与误码测试模块的通信都能正确传输。为适应高速测试,目前SPI的传输速率(指SCK频率)为2 MHz。根据本方案设计误码检测仪已运用于EPON光收发模块的连续码测试。与台湾宜捷威科技的FMTS-3000以及安立的MP1630的测试比较结果看,本误码测试仪其误码数量级与上述两种设备基本一致,但是不能支持突发误码的测试。对突发误码测试的支持是项目组下一步研究的目标。

结 语

VSC8228芯片支持速率多样,它内置PBRS及其他码型的产生及探测模块。笔者利用该特点设计出一种基于C8051F005单片机的廉价高速误码仪,探讨了利用Delphi里的SPCOMM控件来实现PC机与C8051F005之间串行通信的方法,以及C8051F005与VSC8228的SPI通信过程。设计的误码仪支持的测试码型有27、223、231的伪随机码,40或64位用户定义码型以及光纤信号CRPAT、CJT-PAT、CSPAT码型等,一次可测误码高达43亿个,可测码速高达4.25 Gbps在EPON光收发模块中实现了误码测试,效果较好,而且功耗低,有较高的实用价值。