主要内容:

·DMA介绍

·DMA操作

·DMA寄存器

直接存储器存取(DMADirect Memory Access)方式是用硬件实现存储器与存储器之间或存储器与I/O设备之间直接进行高速数据传送,不需要CPU的干预。这种方式通常用来传送数据块。MSP430F54x系列单片机内部含有DMA模块,而且几乎内部所有外设都可以触发DMA开始存取数据。

1.1DMA 的特性

DMA模块有以下特点:

数据传送不需要CPU介入,完全由DMA控制器自行管理。在整个地址空间范围内传输数据;能够提高片内外设数据吞吐能力,实现高速传输,每个字或者字节的传输仅需要2个MCLK;

减少系统功耗,即使在片内外设进行数据输入或输出时,CPU也可以处于超低功耗模式而不需唤醒;

字节和字数据可以混合传送:DMA传输可以是字节到字节、字到字、字节到字或者字到字节。当字到字节传输时,只有字中较低字节能够传输,当从字节到字传输时,传输到字的低字节,高字节被自动清零;

四种传输寻址模式:固定地址到固定地址、固定地址到块地址、块地址到固定地址以及块地址到块地址;

触发方式灵活:边沿或者电平触发。单个、块或突发块传输模式:每次触发DMA操作,可以根据需要传输不同规模的数据

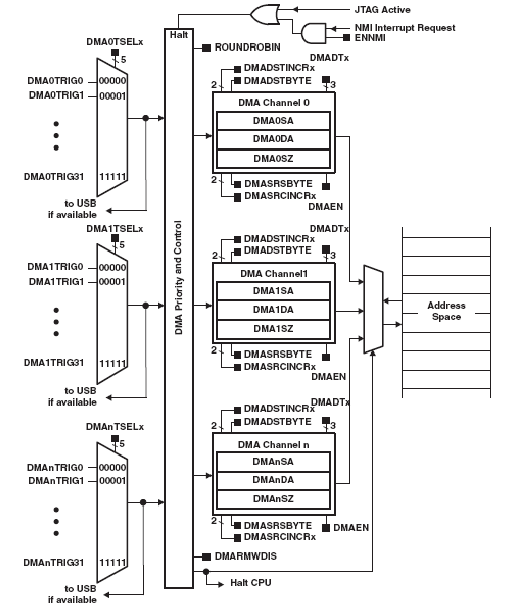

1.2DMA 控制器结构框架图

2,DMA 操作

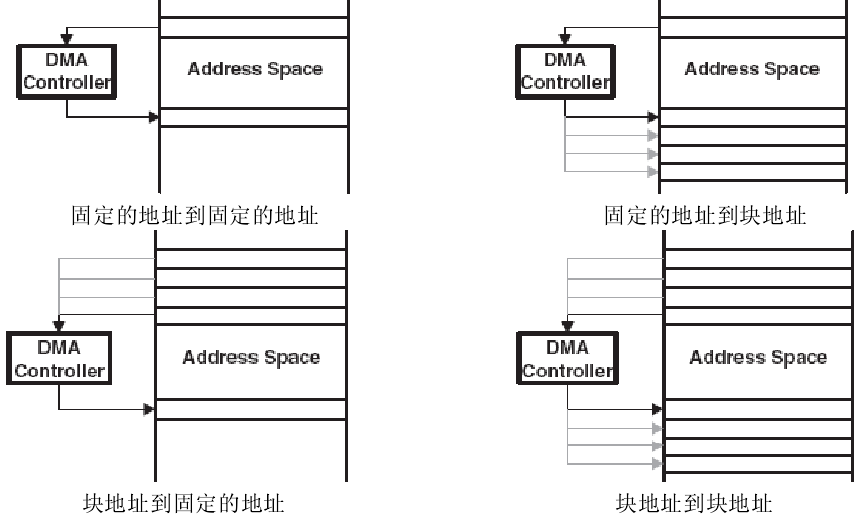

2.1DMA寻址方式

DMA 控制器有四种寻址方式。

·固定的地址到固定的地址

·固定的地址到块地址

·块地址到固定的地址

·块地址到块地址

对于每个 DMA 通道的寻址方式都是独立可配置的。例如,通道 0 可以在两个固定的地址间传输,而通道 1 可在两个块地址间传输。

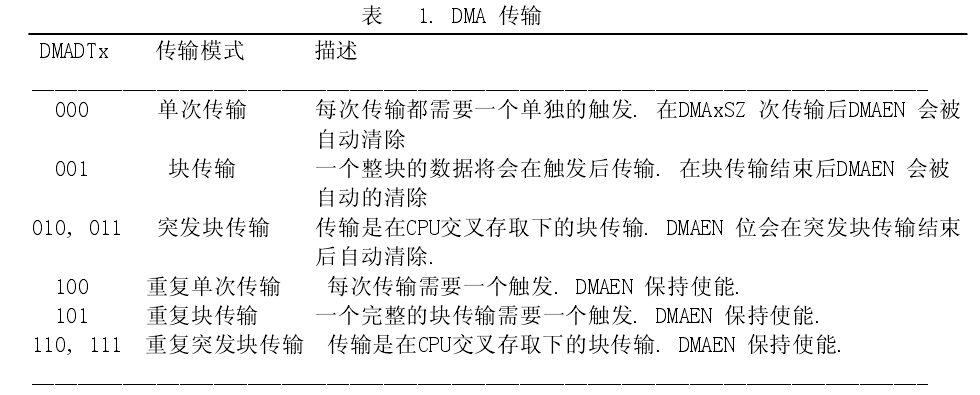

2.2DMA 传输模式

DMA有六种传输模式:单字或者单字节传输;块传输;突发块传输;重复单字或者单字节传输;重复块传输;重复突发块传输。前三个,传输完成后DMAEN自动复位;再次传输时需要重新置位DMAEN位以使能DMA通道。后三个为重复模式,一次传输完成后,DMAEN不复位;再次出发时,可以再次启动数据传输。

六种传输模式通过DMADTx寄存器设置。每个通道都可以独立的配置其传输模式。例如,通道 0 可以配置为单次传输模式,而通道 1 可以配置为突发块传输模式,通道 2 配置为重复块传输模式。传输模式的配置和寻址方式是独立的任何寻址方式都可以使用每种传输模式。

2.3DMA 初始化

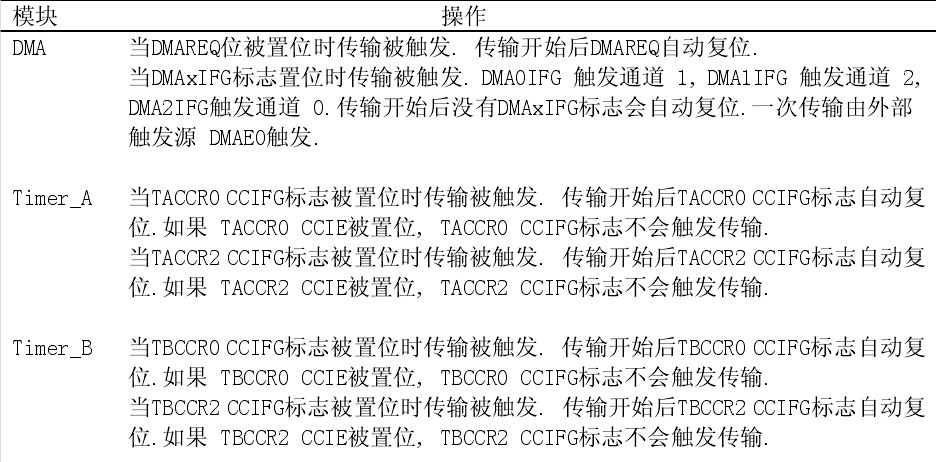

上表 描述了部分模块类型的触发操作。请参阅特殊器件的可用的触发列表的数据表,以及它们各自的 DMAx TSELx 值。

每个通道的触发源有DMAxTSELx位进行控制的,这些位必须在DMAEN位为0时进行设置,否则可能出现不可预料的DMA触发。

当选择一个触发时,必须确保触发还没有发生或者将不会发生。

跳变触发

当 DMALEVEL = 0 时,跳变触发将被选择并且上升沿触发信号启动传输。在单次传输模式中,每次传输都需要一次触发。当使用块或者突发块模式时,仅需要一个触发来启动块或者突发块传输。

电平触发

当 DMALEVEL = 1 时,电平触发被选择。为了适当的操作,电平触发仅用在当外部触发 DMAE0 被选做触发源时。只要触发源信号为高电平就会有 DMA 传输被触发并且 DMAEN 位保持置位。

为了保证块或突发块传输结束,触发信号必须保持为高电平。在块或突发块传输时,如果触发信号变低,DMA 控制器将会保持在当前状态直到触发源信号变高或者直到 DMA 寄存器被软件修改。如果 DMA 寄存器没有被软件修改,当触发信号再次变高时,传输将会恢复到触发信号变低的那个状态。

当 DMALEVEL = 1 时,选择传输模式时推荐 DMADTx = {0, 1, 2, 3}因为 DMAEN 位是在传输结束后自动置位的。

2.4DMA 通道优先权

默认的 DMA 通道优先权顺序是从 DMA0 到 DMA7。如果两三个触发同时发生或者未被解决,最高优先权的通道将会首先完成传输(单次,块或者突发块传输),然后是第二优先权的通道,最后是第三优先权的通道。较高优先权的通道被触发后将不会在进行中的传输中被停止。等到进行中的传输结束后较高优先权的传输即开始。

DMA 通道的优先权由 ROUNDROBIN 位配置。当 ROUNDROBIN 位被置位时,传输完成的通道的优先权变为最低。通道的优先权总保持相同,举个三个通道的例子 DMA0-DMA1-DMA2:

当 ROUNDROBIN 被清除时,通道的优先权回到默认。

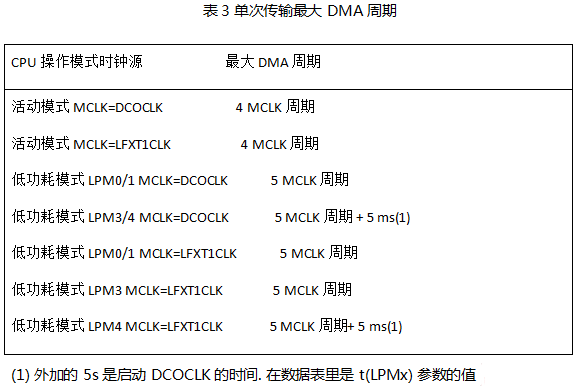

2.5DMA 传输周期

在每次单传输或者块传输或者突发块传输时 DMA 控制器需要一个或两个 MCLK 时钟周期来同步。同步后每个字节/字需要两个 MCLK 时钟周期来传输,传输后有一个周期的等待时间。因为 DMA控制器使用 MCLK,DMA 周期决定于 MSP430 的操作模式和时钟系统的设置。

如果 MCLK 时钟活动,但是 CPU 关闭,DMA 控制器将使用 MCLK 时钟来完成每次传输,无需重新使能 CPU。当 MCLK 时钟关闭时,DMA 控制器将临时开启 MCLK 时钟,以 DCOCLK 为时钟源,以完成单次或者整个块或者突发块传输。在每次传输结束后,CPU 继续保持关闭,MCLK 关闭。各种操作模式下的最大 DMA 周期见表 3。