·16位定时器B之结构

·16位定时器B之寄存器

·16位定时器B之程序举例

1. 16位定时器B之结构

1.1 Timer_B7系统

16位Timer_B7仅在MSP430F14x及MSP430F44x芯片中存在,从标题的命名规则可知Timer_B具有7个捕获/比较器。与Timer_A3相比,Timer_B7还具有一下特点:

1、Timer_B7可以配置定时器计数长度:8位、10位、12位或16位;

2、Timer_B7捕获/比较寄存器增加了锁存器;

3、Timer_B7不具备SCCI控制位及其相关功能;

4、Timer_B7在进行比较时,并不是TBCCRx中的值直接与TBR比较,二十从TBCCRx锁存到对应的锁存器TBCLx中与TBR进行比较。

除此之外,Timer_B7也具有中断能力,中断可以由计数器溢出产生,或者由捕获/比较寄存器产生。

1.2计数部分结构

Timer_B7的功能结构可以分为三部分:可控制计数长度的计数器部分、捕获/比较寄存器部分和输出单元。

我们现在看到的框图是可控制计数长度的计数部分,它是由时钟源选择,输入分频器模式控制以及计数器部分组成的。

1.3捕获比较模块

Timer_B7具有7个捕获/比较模块:利用捕获模块可以用来捕获事件的发生时间;利用比较模块可以输出定时结果或者配合输出单元产生特定的信号。

在图中捕获/比较控制与寄存器结构中明确的标示出来各个控制寄存器与信号之间的控制关系,捕获/比较模式受对应的TBCCTLx中的CAP位控制,这里不再讲述。

输出单元与Timer_A3相同,这里也不再赘述。

1.4 定时器模式

在介绍TBCTL中的MC1和MC0控制位时提到,收到MC1和MC0位的共同控制,使得Timer_B7共有4种定时器的工作模式,在实际的使用中,这4种模式的影响非常广泛,因此下面我们将详细的介绍着四种工作模式,这四种工作模式是:

※MC_0:停止模式

※MC_1:增计数模式

※MC_2:连续计数模式

※MC_3:增减计数模式

2.16位定时器B之寄存器

2.1Timer_B7控制寄存器

Timer_B7系统共用17个寄存器,所有对于Timer_B7执行的相关操作都通过读写相关的寄存器实现。这17个寄存器可以归类为TBCTL、TBCCTLx、TBCCRx、TBR、TBIV和TBCLx寄存器组成,其中TBCTL包括了Timer_B计数器中控制位和状态位;TBCCTLx控制捕获/比较寄存器和比较器;TBCCRx保存Timer_B捕获或比较的数据;TBR是16位计数器的计数执行单元,保存了计数器的内容;TBIV保存了中断请求的中断信息;相对于Timer_A3系统,Timer_B7多出了一个TBCLx寄存器,即前面说到的Timer_B7在进行比较时与Timer_A3的差别。

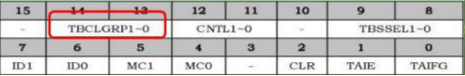

2.2 TBCTL控制寄存器

TBCTL是一个16位寄存器,其中第15、10位和第3位没有使用其他位在POR后全部复位,但不受PUC影响。

TBCLGRP1|TBCLGRP0:比较装载模式组控制寄存器,由于前面已经提到过“Timer_B7在进行比较时,并不是TBCCRx中的值直接与TBR比较,二十从TBCCRx锁存到对应的锁存器TBCLx中再与TBR进行比较”,因此,就需要决定在什么条件下、以何种模式组方式将TBCCRx的值锁存到对应的TBCLx中。该两个控制位决定了以何种模式组方式装载TBCLx。3:将TBCTL1~TBCTL6作为单独一组,由TBCCTL1中的CLLD定义装载条件;2:将TBCTL1~TBCTL3作为第一组,由TBCCTL1中的CLLD定义装载条件;将TBCTL4~TBCTL6作为第二组,由TBCCTL4中的CLLD定义装载条件。1:将TBCTL1~TBCTL2作为第一组,由TBCCTL1中的CLLD定义装载条件;将TBCTL3~TBCTL4作为第二组,由TBCCTL3中的CLLD定义装载条件;将TBCTL5~TBCTL6作为第三组,由TBCCTL5中的CLLD定义装载条件。0:不分组,由对应的TBCCTLx中的CLLD定义装载条件。

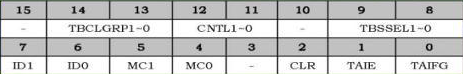

2.3TBCTL控制寄存器

CNTL1|CNTL0:计数器最大计数长度。3:计数器最大计数长度为8位,即0xFFH。2:计数最大长度为10位,即0x03FFH;1:计数最大长度为12位,即0x0FFFH;0:最大计数长度为16位,即0xFFFFH。

TBSSEL1|TBSSEL0:选择输入到分频器的时钟源。3:INCLK,外部输入时钟(即MSP430F149的P2.1)。2:SMCLK,子系统时钟;1:ACLK,辅助系统时钟。0:TACLK,外部引脚输入信号(即MSP430F149的P1.0)。

ID1|ID0选择输入到分频器的时钟源。3:1/8分频;2:1/4分频;1:1/2分频;0:不分频。

MC1|MC0:选择定时器工作模式。3:增减计数模式;2:连续计数模式;1:增计数模式;0:停止模式。

TBCLR:计数器清零。

TBIE:定时器溢出中断允许位。

TBIFG:定时器溢出标志。

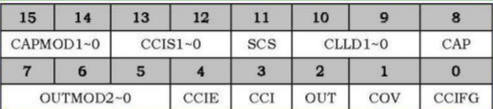

2.4TBCCTLx捕获/比较控制寄存器

每一个TBCCTLx控制寄存器共有16位,在POR后复位,但不受PUC的影响。

CAPMOD1|CAPMOD0:捕获模式选择。3:上升沿捕获和下降沿捕获;2:下降沿捕获;1:上升沿捕获;0:禁止捕获模式。

CCIS1|CCIS0:捕获事件的信号输入源。3:选择Vcc为捕获事件的信号输入源;2:选择GND为捕获事件的信号输入源;1:选择CCIxA为捕获事件的信号输入源;0:选择CCIxB为捕获事件的信号输入源。

SCS:捕获信号与计数器时钟是否同步。1:同步捕获;0:异步捕获。

CLLD1|CLLD0:设定TBCLx装载方式,决定了在什么条件下将TBCCRx的值锁存到对应的TBCLx中去。3:当TBR计数到TBCL0时,TBCCRx的值自动装载到TBCLx中;2:连续计数模式下TBR计数到0时执行自动装载;增减计数模式下TBR计数到TBCL0或者0时执行自动装载。1:TBR数到0时执行自动装载;0:立即执行自动装载。

CAP:捕获/比较模式选择。1:捕获模式;0:比较模式。

OUTMOD2|OUTMOD1|OUTMOD0:选择输出单元的输出模式。7:PWM复位/置位模式;6:PWM翻转/置位模式;5:复位模式;4:翻转模式;3:PWM置位/复位模式;2:PWM翻转/复位模式;1:置位模式;0:输出模式。

CCIE:中断允许位。1:允许中断;0:禁止中断。

CCI:用户可以从此位读出在捕获模式中选择捕获事件的输入信号源。

OUT:输出信号控制位。用来控制在输出0模式下OUTx的输出信号。1:输出高电平;0:输出低电平。

COV:捕获寄存器溢出标志位。当捕获寄存器中的值在用户读出前,再次发生捕获事件,则该位置位,置位后用户需要软件对该标志位复位。

CCIFG:中断标志位,在不同的模式下该中断标志位置位表示不同的意义。捕获模式下,表示TBCCRx中保存了捕获到的TBR值。比较模式下,表示TBR中的值等于TBCCRx中的值。

2.5 TBCCRx捕获/比较寄存器

该寄存器在不同的模式下具有不同的意义:

捕获模式下,在外部输入信号满足捕获条件时,则系统将TAR中的数据保存到CCRx寄存器中;

比较模式下,用户根据预先设定的时钟源、分频系数和定时周期工作模式,向CCRx中写入定时长度。

TBR计数器中保存了16位计数器当前的数值。

2.6TBIV中断向量寄存器

我们现在看到的表格是TBIV中断表。

TBIV中保存了中断请求的中断源,保存了Timer_B7的中断向量仅占用了该寄存器的第3~1位。

3.16位定时器B之程序举例

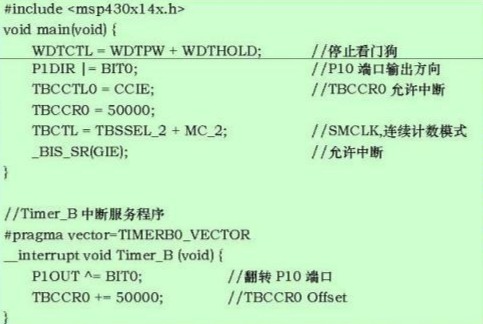

3.1连续计数模式下中断端口翻转

程序允许P1.0端口输出,设置TimerB工作在连续计数模式下,开启TBCCR0中断和总中断;在对应的中断服务程序中翻转P1.0端口的输出并设置TBCCR0的偏移量。

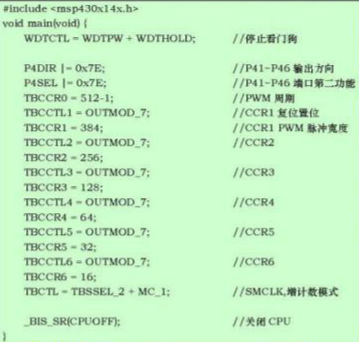

3.2增计数模式下端口输出翻转

程序设置Timer_B7工作在增计数模式下、TBCCR6~TBCCR7为PWM复位/置位模式以输出6路周期相同、占空比不同的PWM信号。按照增计数模式的计数规律:PWM周期为512个Timer_B7的时钟周期,则P4.1~P4.7输出PWM的占空比分别为75%、50%、25%、12.5%、6.25%、3.125%。