1,MSP430F14x的内部结构

这里是MSP430F14x的硬件乘法器。它通过内部总线与CPU相连,特别适用于对运算要求很严格的情况。操作结果可以在操作数装入硬件乘法器后立即处理。无需额外的时钟周期,大大提高了MSP430系列单片机的运算速度,提高了数据处理能力,拓宽了其应用范围。

2,硬件乘法器

硬件乘法器是16位外围模块,并不集成在CPU内,它的运行独立于CPU,也不需要特殊的指令。运行时只需要将操作数装入它的寄存器,在下一条指令既可以得到运算结果,不需要额外的等待周期。硬件乘法器在不改变MSP430的基本机构的情况下增强了它的功能。

支持的乘法运算:

※16位x16位,16位x8位,8位x16位,8位x8位;

※无符号乘法(MPY);

※有符号乘法(MPYS);

※无符号乘加(MAC);

※有符号乘加(MACS)。

3,硬件乘法器的结构

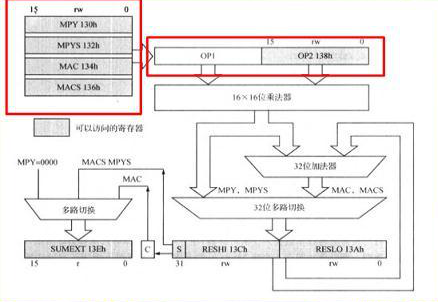

我们现在看到的这张图是硬件乘法器的结构图。

硬件乘法器的乘数来源于两个操作数寄存器:OP1和OP2,OP1可来源于四个寄存器:MPY,MPYS,MAC及MACS。当第一个操作数写入OP1时,乘法的类型就已经被确定了,当用户写入第二个操作数时,乘法操作便开始执行,并在用户用变址寻址模式读结果寄存器前结束。如果用户采用间接寻址或间接增量寻址模式指令读结果寄存器,必须在写第二个操作数与读结果寄存器的两条指令之间插入一条指令。相乘的结果保存在3个结果寄存器中,即结果高字寄存器RESHI、结果低字寄存器RESLO和结果扩展寄存器SUMEXT。寄存器RESHI和RESLO的内容为两个16位数相乘的32位乘积结果。而寄存器SUMEXT的内容由执行的乘法模式及乘积的结果确定。

4,硬件乘法器的寄存器

硬件乘法器的结构主要包括操作数寄存器和结果寄存器,如下所示:

MPY 操作数1 ,表示操作数为无符号数乘

MPYS 操作数1 ,表示操作数为有符号数乘

MAC 操作数1, 表示操作数为无符号数加

MACS 操作数1, 表示操作数为有符号数加

OP2 操作数2

RESLO 结果低字节存储器

RESHI 结果高字节存储器

SUMEXT 结果扩展寄存器

5,硬件乘法器的应用

硬件乘法器的操作一般按照以下步骤进行:

1、写第一个操作数OP1,来源于四个寄存器之一;

2、写第二个操作数OP2,写入完毕,立即开始乘法运算;

3、读结果,乘法运算存放在RESHI、RESLO和SUMEXT中。

6,硬件乘法器的应用

在进行硬件乘法器操作时,应注意:

1、当第二个操作数写入完毕时,乘法运算就开始执行,一般在取出结果之前插入1-2条指令,以保证运算时间的需要。

2、在一个器件中只有一个硬件乘法器,如果遇到多出使用的情况,必须在前一次使用完成后再进行下一次。

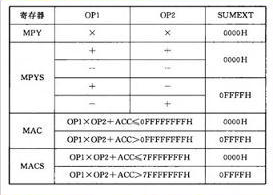

3、结果扩展寄存器SUMEXT的内容与运算类型及结果都有关系。

4、无论进行何种计算,只要操作数类型为8x8型,操作过程就要使用寄存器的绝对地址,而不能使用符号形式,但是16x16位运算可以使用寄存器符号形式。

如果在写入第一个操作数和第二个操作数之间发生中断,并且硬件乘法器在中断服务程序中被使用,则原来选择的乘法模式丢失,产生不可预料的结果。为了避免这种情况的发生,如果在中断服务程序中使用硬件乘法器,则在主程序中使用硬件乘法器前关闭中断。