磁通门传感器最早于1935年发明并投入应用,用于静态或者低频变化的弱磁检测,拥有其他磁敏元件难以媲美的灵敏度和可靠性,在磁场测量领域一直占据着不可替代的位置。磁通门传感器适用于地磁或人体磁场的检测,在航空、航天、地质勘探、医疗卫生等领域有着广泛的应用。

本文引用地址:http://www.21ic.com/app/eda/201810/799212.htm

磁通门传感器探头通常采用类似于变压器的双铁芯结构,利用软磁铁芯变化磁导率的特性将被测磁场调制成激励信号的偶次谐波。信号处理系统对探头输出加以处理,从中提取与被测磁场大小相关的信号,转换成直流量并输出。

传统的磁通门信号处理电路采用模拟元器件,温度性能严重地受到影响,且很难小型化,可移植性也很差。与之相比,现代数字磁通门系统,温度性能稳定,体积小,可移植性强。根据应用的具体情况,可选的实现方式多样,有单片机、可编程数字逻辑,或数字信号处理(DSP)芯片等。

FPGA(Field Programmable GateArray)是一种高速的可编程逻辑芯片,具有其他设备难以比拟的灵活性,其大部分引脚的功能、内部电路结构完全由用户根据需要定义。FPGA器件具有很高的实用价值,一方面可以作为专用集成电路的替代品,直接在最终产品中使用,另一方面,也可以在专用集成电路开发流程中,做行为验证工具。

在本文中,描述了一种基于FPGA的磁通门系统的实现,系统采用闭环结构,对磁通门传感器探头输出的数据进行实时处理,提取出反映被测低频磁场大小的直流信号。

1 磁通门系统结构和工作原理

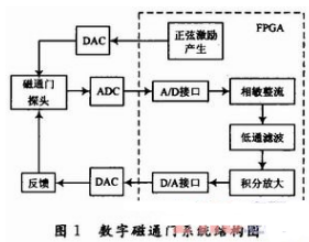

如图1所示,整个系统的硬件包括磁通门传感器探头,DAC,ADC和FPGA。功能上可分为传感器激励源、磁通门信号解算、负反馈回路三个模块。

FPGA内的正弦激励发生电路和外部DAC一起构成传感器激励源模块。高速ADC和FPGA内的A/D接口、相敏整流、低通滤波电路构成磁通门信号解算模块。积分放大、D/A接口、高速DAC,以及反馈网络共同构成了负反馈模块。

系统工作时,在激励信号的驱动下,磁通门探头的感应线圈感应环境磁场大小,产生磁通门信号,经隔直滤波后通过高速ADC芯片转换成串行数据送FPGA的处理。在FPGA中,ADC芯片采集到的串行数据先转换成并行数据,然后通过相敏整流、低通滤波后得到直流信号。低通滤波的结果积分放大后经D/A接口转换成串行数据送高速DAC芯片转换成模拟信号,经反馈电阻反馈到磁通门探头的补偿线圈(即感应线圈),抵消环境磁场。

由于采用闭环结构,前向通道上积分放大环节的增益可视作无穷大,根据自动控制原理,整个系统是无差系统,传感器探头实际上工作在“零场”条件下,反馈电流产生的磁场和环境磁场大小相的方向相反,D/A的前端信号,即积分放大环节的输出反映被测磁场的大小。整个系统的信号梯度主要取决于反馈系数的大小,具有良好的线性度。

2 磁通门信号的特点和处理方法

磁通门系统的核心是信号处理电路。

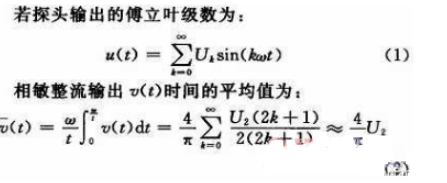

磁通门传感器探头输出的偶次谐波(以二次为主)是有用的磁通门信号,而其他频率的信号都是有害噪声。在实际应用中,通常采用“相敏整流-低通滤波”方法处理磁通门信号。首先用相敏整流进行频谱的调整,通过采用与二次谐波同频率的方波基准乘传感器探头的输出,将二次谐波磁通门信号转换为直流分量,然后用低通滤波滤除其他频率分量,得到反映被测磁场大小的直流量。

低通滤波器输出是相敏整流结果的直流分量,与磁通门传感器探头输出的二次谐波的幅值线性相关,反映被测磁场大小。

3 硬件电路设计

在该设计中,FPGA芯片选用Altera公司CYCLONEⅡ系列的EP2C35F626C5,工作速度快,可定义引脚丰富,逻辑单元数量可观,性价比高。FPGA的工作时钟为50MHz。

磁通门激励起到驱动传感器工作的作用,由D/A模块转换FPGA输出的正弦数字信号产生;本设计中,激励频率为3.051kHz,是FPGA工作时钟的64×256分频,速度相对较低,且精度要求不高,故DAC采用12位并口DA1210芯片。

在闭环系统的前向通道中,A/D模块是偏差检测环节,对传感器探头输出进行采样。该设计中,二次谐波一个周期采样128个点,即ADC采样频率是探头输出二次谐波频率的128倍,也就是781.25kHz。采用AD7980芯片作为A/D转换器,该芯片具有16位精度,转换速度高达1MSPS,可以满足要求。

在反馈回路中,D/A模块作为低频补偿环节,需要具有较高的精度,而转换速率可以较低;该设计采用DA8552芯片,具有16位精度和100KSPS的转换速率。

4 FPGA内部电路设计

4.1 A/D接口和D/A接口

由于前向通道的ADC芯片、反馈回路的DAC芯片都采用串口通信,因此设计了专用的A/D接口和D/A接口,实现了A/D输入和D/A输出的串并/并串转换。

4.2 正弦激励发生

正弦激励发生采用查表的方式实现。用12×256b的ROM存一幅12位正弦波表,以FPGA时钟频率的1/64,即781.25kHz扫描,产生3.051kHz的12位数字正弦信号。

4.3 磁通门信号解算和积分放大

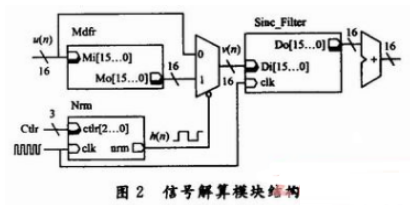

磁通门信号的解算是FPGA内数字逻辑最核心的功能,由相敏整流器、基准发生器和FIR数字滤波器三部分共同实现,如图2所示。

相敏整流器由数据转换器和数据选择器构成。数据转换器.Mdfr将输入u(n)转换成补码形式。输出v(n)是输入u(n)或者其补码,由基准h(n)当前的值决定。实际上,电路的功能等价于将u(n)和在1和-1间交替变化的数列相乘,也就是说,v(n)是u(n)以h(n)为基准相敏整流的结果。

基准发生器Nrm为相敏整流器提供基准h(n)。对50MHz时钟进行分频,产生与二次谐波磁通门信号同频率,即6.103MHz的方波,通过控制信号Ctlr调整相位,使基准的相位和二次谐波磁通门信号的相位对其相敏整流的效率最大化。

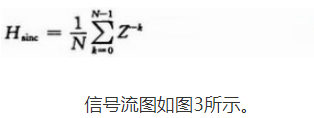

低通滤波器Sinc_Fltr是N点sine滤波器的FIR形式,传输函数是:

由于二次谐波磁通门信号一个周期采样128点,因此N=128;按照图3所示的信号流图,128点sinc滤波器由127个加法器和128个寄存器组成。为防止溢出,加法器和寄存器宽度为16+log28=24位,最后一级输出的高16位作为滤波器的输出。实现了低通滤波的功能。

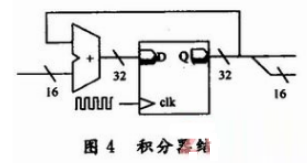

积分放大由积分器Intgtr实现,结构如图4所示。为防止溢出,采用32位的加法器和寄存器。加法器的一个输入端是低通滤波器的输出,另一个是累加和。在闭环系统中,积分器输出的低16位是反映被测磁场大小的数字量。

5 实验和结果

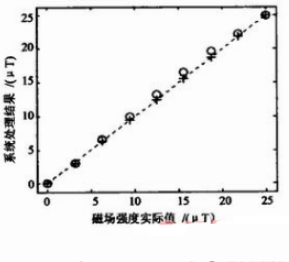

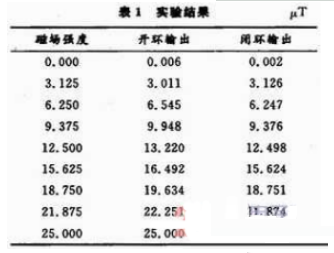

使用双铁芯结构磁通门探头感应被测磁场,磁场强度从0μT变化到25μT。首先去掉积分模块打开反馈回路,对开环结构的前向通道进行测试,然后加入积分模块和闭合反馈回路,对闭环系统进行测试。两次实验的输入/输出关系如图5所示,图中“o”是开环结构的结果,“+”是闭环结构的结果。

两次试验的数据如表1所示。

当系统开环时,随着被测磁场的增大,系统输出单调增高,可以反映被测磁场的大小。输出的非线性度为4.01%,最大误差为0.867μT,受磁通门探头铁芯的非线性影响很大。闭环后,系统非线性度和误差性能得到明显改善,非线性度为0.012%,最大误差为3nT。

6 结语

本文中描述的基于FPGA的磁通门传感器系统采用闭环结构,提高了系统输出梯度线性度。FPGA内的数字逻辑实现了包括磁通门信号解算在内的多种功能。实验验证了系统功能的正确性。由于数字逻辑的特点,和模拟系统相比,基于FPGA的设计有着优秀的温度稳定性,可移植性,且易于小型化。本文中的设计可直接应用在最终产品中,也可以作为专用集成电路的行为验证,以此为基础继续开发集成电路芯片。