引言

绿色环保节能是全球化的热潮,而嵌入式计算机系统被广泛应用于便携式和移动性较强的产品,低功耗设计不仅是绿色环保的要求,也是嵌入式计算机系统体积和质量的约束。随着市场对嵌入式计算机系统在体积和性能方面要求的不断提升,小体积、高性能与有限的电池能量之间的矛盾曰益突出,系统低功耗设计是解决这一矛盾的有效手段。基于ARM的嵌入式计算机系统在保证系统性能的情况下通过硬件和软件两方面低功耗的设计来最大限度地降低嵌入式计算机系统的功耗。

1 系统组成

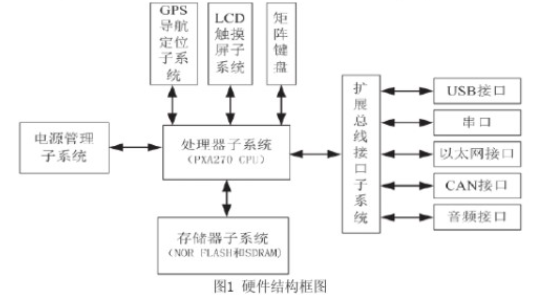

嵌入式计算机系统采用ARM9微处理器PXA270为核心,外围扩展了许多标准的IO接口来实现系统功能,如显示、数据采集、定位、通信等功能。系统主要由处理器子系统、存储器子系统、电源管理子系统、GPS导航定位子系统、LCD触摸屏子系统、矩形键盘和扩展总线接口子系统等组成,扩展的标准IO接口包括USB接口、串口、以太网接口、CAN接口、音频接口等,硬件结构框图如图1所示。由于嵌入式计算机系统不能一直有充足的电源供应,需用电池来供电,所以设计过程中需要从各个细节考虑降低功率消耗,从而延长电池使用时间。如图1所示,系统随着实现功能的增多相应的功耗也会增大,根据系统组成主要的功耗在于微处理器、LCD触摸屏、集成电路、电阻和有源器件等,设计过程中需要从全局来考虑功耗的设计,下面将详细描述功耗产生的原因和低功耗的设计与实现。

2 功耗产生的原因

如图1所示的嵌入式计算机系统硬件架构中,功耗主要来源于以下几个方面:微处理器、LCD触摸屏、集成电路、电阻和有源器件等。其中微处理器是系统功率消耗的主要来源,它几乎占据了除LCD触摸屏以外的整个系统功耗的一半以上,所以选择低功耗的微处理器对于系统的功耗大小有举足轻重的影响。LCD触摸屏是嵌入式系统中功耗的另一个主要来源。除了微处理器和LCD触摸屏之外,集成电路是系统组成的主要器件,对应的电路中只要有电流流过,就会产生功耗。集成电路的功耗主要包括开关功耗、静态功耗、动态功耗、短路功耗和漏电功耗,对于目前大多数采用CMOS工艺的集成电路来说,主要的功耗是动态功耗,是指电路翻转时产生的功耗,它是由于电路翻转时存在跳变沿,在翻转的瞬间,电流较大,所以动态功耗较大。除此之外,电阻和有源器件也是系统中功耗产生的一个原因,尤其在有源器件的状态变化时产生较大的电流和电压,引起较大的功率消耗。另外,CMOS电路中最大的功耗来自于内部和外部的电容充放电产生的功耗。

据功耗产生的原因,结合实际的应用环境,本设计的嵌入式计算机系统通过硬件和软件的低功耗设计来实现系统的低功耗,下面详细描述。

3 硬件的低功耗设计与实现

3.1 低功耗的微处理器选择

如前所述,嵌入式计算机系统的微处理器是系统功耗的主要来源,所以在选择微处理器即CPU时,不仅要注意微处理器的性能优劣(比如时钟频率)及提供的接口和功能多少,对于嵌入式计算机系统来说也要注重微处理器的功耗特性。微处理器的功耗包括内核消耗功耗和外部接口消耗功耗,内核消耗功耗主要体现在供电电压和时钟频率的高低;外部接口消耗功耗体现在专门I/O控制器的功耗。

在本系统的设计中通过对微处理器的性能和功耗的比较和衡量,我们选择了低功耗的微处理器PXA270,PXA270的主频可以设置在104MHz到624MHz之间;PXA270嵌入式处理器在个人的互联网客户端架构处理器(PCA)中集成无线MMX技术,使得它拥有高性能、低功耗的多媒体加速能力,能够很好地支持MPEG4和MP3解码;同时加入了IntelSpeed Step动态电源管理技术,在保证CPU性能的情况下,最大限度地降低小型嵌入式计算机系统的功耗。

3.2 接口电路的低功耗设计

嵌入式计算机系统的接口电路的低功耗设计主要体现在以下几个方面:

(1)选择静态电流较低的外围芯片,设计中除考虑系统的功能实现以外,在外围接口芯片如USB接口、串口、以太网接口、CAN接口、音频接口的设计芯片都尽量选择静态电流较低的芯片来实现系统功能。

(2)恰当地选择上拉电阻/下拉电阻。对于嵌入式计算机系统的接口电路设计,许多信号管脚都涉及上拉电阻或下拉电阻,在设计中考虑能正常驱动后级信号的情况下,上拉电阻或下拉电阻尽量选择较大的阻值。如同样是在3.3V的系统中用10kΩ的上拉电阻比用4.7kΩ的上拉电阻,当输出为低时,每只脚上的电流消耗少0.37mA,若系统设计中存在100个这样的管脚,就减少了37mA的电流。系统的接口电路中多数情况为低的信号设计上用下拉电阻来节省功耗。

(3)悬空脚尽量接地或上拉到VCC。系统中的集成电路基本都是CMOS器件,CMOS器件由于其悬空的输入端的阻抗极高,很可能感应一些电荷导致器件被高压击穿,而且还会导致输入端信号电平随机变化,导致CPU在休眠时不断地被唤醒,从而无法进入休眠状态或出现其他莫名其妙的故障,所以设计上未使用的悬空脚要尽量接地或上拉到VCC,减少不必要的功耗。

(4)慎重选择Buffer。在以往的设计中,设计人员习惯用Buffer来增加电路的驱动能力,这些Buffer肯定会导致更多的功耗。在系统设计中,仔细检查每个芯片的最大输出电流IOH和IOL是否足以驱动下级芯片,通过选取合适的前后级芯片来避免不必要的Buffer,来尽量减少系统的功率消耗。

3.3 电源供给电路的低功耗设计

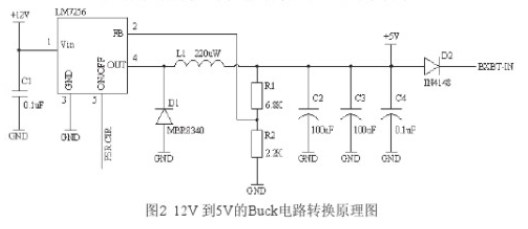

嵌入式计算机系统的电源供给电路需考虑合适的电压变换结构。一般来说,电压变换结构包括线性稳压和DC/DC变换电路两种主要方式,其中线性稳压的特点是电路结构简单,所需元件数量少,输入和输出压差可以很大,但其致命弱点就是效率低、功耗高。其效率完全取决于输出电压大小。DC/DC变换电路的特点是效率高、升降压灵活,但缺点是电路相对复杂,干扰较大。一般常见的DC/DC变换电路由Boost和Buck两种电路,其中Boost电路用于升压,Buck电路用于降压。

图2所示是嵌入式计算机系统采用的12V转换到5V的DC/DC变换电路图,其控制芯片采用国家半导体(NS)的LM2576,实际是采用Buck电路,其MOSFET和相关的控制电路位于芯片内部。

图3所示为12V到5V转换电路的转换效率图,如图所示当输入为12V,输出为5V时,转换效率约为77%(ILOAD=3A),差不多为线性稳压器转换效率的一倍。

在嵌入式计算机系统的电源部分设计选择了DC/DC转换电路(LM7256S)将12V转换为5V,12V转换为3.3V供系统使用,这种处理方式有效的节约了能源,降低了整机的功耗。

4 软件的低功耗设计与实现

4.1 动态设置时钟频率

对于已经搭建好的硬件系统来说,系统已经定型,从硬件设计上已不能做更多的考虑,这时我们只能从软件入手来实现系统的低功耗设计。而对于软件的低功耗设计最切实可行的就是实现动态电源管理,所谓动态的电源管理就是在系统运行期间通过对系统的时钟或电压的动态控制来达到节省功率的目的,这种动态控制是与系统的运行状态密切相关的。

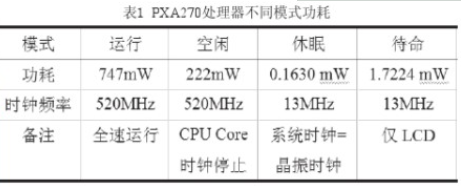

在嵌入式计算机系统中,软件设计上动态地通过设置时钟频率来降低系统的功耗,换句话说就是为系统选取合适的工作模式。系统采用的微处理器是ARM处理器PX270,PXA270处理器的内部的各种频率都是通过外部晶振频率经内部锁相环(PLL)倍频后产生的,可通过内部的寄存器设置各种工作频率来控制功耗。PXA270处理器共有四种工作模式:正常模式、空闲模式、休眠模式、待命模式,各种模式的功耗如表1所示。

由表1可见,PXA270在全速运行的时候比在空闲或者休眠的时候消耗的功率大得多。省电的原则就是让正常运行模式远比空闲、休眠模式少占用时间。在嵌入式计算机系统中,系统在全速运行的时候远比空闲的时候少,所以设计上可通过设置使PXA270尽可能工作在空闲状态,然后通过相应的中断唤醒PXA270恢复到正常工作模式,处理响应的事件,然后再进入空闲模式。这样的软件设计方式可尽可能地降低系统的功耗。

4.2 动态控制外设控制寄存器

PXA270处理器提供的接口控制器很多,如ADC、I2C、I2S、LCD、Flash、Timer、UART、SPI、USB等,实际应用中只使用了部分功能,ADC、I2C、I2S和SPI都没有用到,为节省系统功耗,需动态地关注这些接口控制器的状态,及时关闭不需要的外设控制器,因为若不将不用的接口控制器关闭,即使它们没有处于工作状态,仍然会消耗电流。软件通过CLKCON寄存器的设置,关闭不需要的功能模块,经测量可节省2mA的电流。另外,动态关闭一些仍然需要的外设控制器来进一步节省能量。

如在空闲模式下,PXA270内核停止运行,我们还可以进一步关闭一些其他的外设控制器,如USB、SDI、FLASH等,只要保证唤醒PXA270的

I/O控制器正常工作即可,如通过UART唤醒,则UART控制器不能被关闭。等到PXA270被唤醒后,再将USB、SDI、Flash等控制器打开。

上述的软件低功耗设计的两种方式,一种是通过改变了系统的时钟频率,另一种是通过控制外设控制器的开关来达到节约能量的目的。除此之外,同时可通过动态改变处理器的电压和频率来进一步节省功率,我们选择的PXA270微处理器就加入了Intel Speed Step动态电源管理技术,在保证CPU性能的情况下,最大限度地降低嵌入式计算机系统的功耗。

5 结束语

嵌入式计算机系统的低功耗设计,本身就是理论和设计实践相结和的问题,要降低功耗,系统中各个环节都不容忽视,这也是一个不断优化的过程。本文的设计中综合考虑各种可能的因素、条件和状态,对各种细节进行认真的斟酌和分析,取得了较为满意的效果,达到降低系统功耗的目的。该设计已在产品应用,性能稳定,功耗较低。