1、电源设计项目前期各个参数注意细节

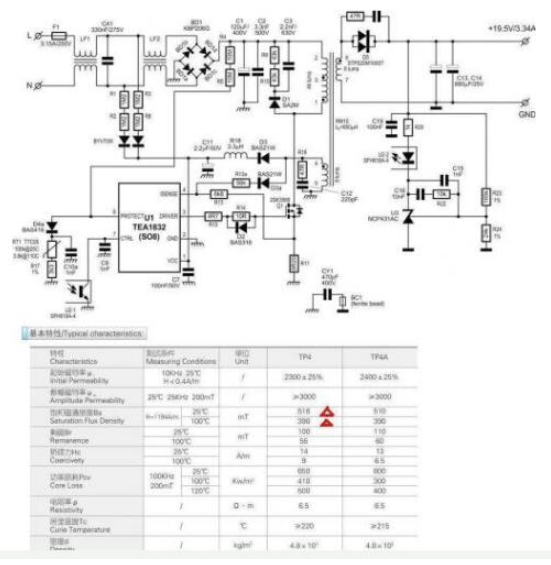

借鉴下NXP的这个TEA1832图纸做个说明。分析里面的电路参数设计与优化并做到认证至量产。 在所有的元器件中尽量选择公司仓库里面的元件,和量大的元件,方便后续降成本拿价格。

贴片电阻采用0603的5%,0805的5%,1%,贴片电容容值越大价格越高,设计时需考虑。

1、输入端,FUSE选择需要考虑到I^2T参数。保险丝的分类,快断,慢断,电流,电压值,保险丝的认证是否齐全。保险丝前的安规距离2.5mm以上。设计时尽量放到3mm以上。需考虑打雷击时,保险丝I2T是否有余量,会不会打挂掉。

2、这个图中可以增加个压敏电阻,一般采用14D471,也有采用561的,直径越大抗浪涌电流越大,也有增强版的10S471,14S471等,一般14D471打1KV,2KV雷击够用了,增加雷击电压就要换成MOV+GDT了。有必要时,压敏电阻外面包个热缩套管。

3、NTC,这个图中可以增加个NTC,有的客户有限制冷启动浪涌电流不超过60A,30A,NTC的另一个目的还可以在雷击时扛部分电压,减下MOSFET的压力。选型时注意NTC的电压,电流,温度等参数。

4、共模电感,传导与辐射很重要的一个滤波元件,共模电感有环形的高导材料5K,7K,0K,12K,15K,常用绕法有分槽绕,并绕,蝶形绕法等,还有UU型,分4个槽的ET型。这个如果能共用老机种的最好,成本考虑,传导辐射测试完成后才能定型。

5、X电容的选择,这个需要与共模电感配合测试传导与辐射才能定容值,一般情况为功率越大X电容越大。

6、如果做认证时有输入L,N的放电时间要求,需要在X电容下放2并2串的电阻给电容放电。

7、桥堆的选择一般需要考虑桥堆能过得浪涌电流,耐压和散热,防止雷击时挂掉。

8、VCC的启动电阻,注意启动电阻的功耗,主要是耐压值,1206的一般耐压200V,0805一般耐压150V,能多留余量比较好。

9、输入滤波电解电容,一般看成本的考虑,输出保持时间的10mS,按照电解电容容值的最小情况80%容值设计,不同厂家和不同的设计经验有点出入,有一点要注意普通的电解电容和扛雷击的电解电容,电解电容的纹波电流关系到电容寿命,这个看品牌和具体的系列了。

10、输入电解电容上有并联一个小瓷片电容,这个平时体现不出来用处,在做传导抗扰度时有效果。

11、RCD吸收部分,R的取值对应MOSFET上的尖峰电压值,如果采用贴片电阻需注意电压降额与功耗。C一般取102/103 1KV的高压瓷片,整改辐射时也有可能会改为薄膜电容效果好。D一般用FR107,FR207,整改辐射时也有改为1N4007的情况或者其他的慢管,或者在D上套磁珠(K5A,K5C等材质)。小功率电源,RC可以采用TVS管替代,如P6KE160等。

12、MOSFET的选择,起机和短路情况需要注意SOA。高温时的电流降额,低温时的电压降额。一般600V 2-12A足够用与100W以内的反激,根据成本来权衡选型。整改辐射时很多方法没有效果的时候,换个MOSFET就过了的情况经常有。

13、MOSFET的驱动电阻一般采用10R+20R,阻值大小对应开关速度,效率,温升。这个参数需要整改辐射时调整。

14、MOSFET的GATE到SOURCE端需要增加一个10K-100K的电阻放电。

15、MOSFET的SOURCE到GND之间有个Isense电阻,功率尽量选大,尽量采用绕线无感电阻。功率小,或者有感电阻短路时有遇到过炸机现象。

16、Isense电阻到IC的Isense增加1个RC,取值1K,331,调试时可能有作用,如果采用这个TEA1832电路为参考,增加一个C并联到GND。

17、不同的IC外围引脚参考设计手册即可,根据自己的经验在IC引脚处放滤波电容。

18、更改前:变压器的设计,反激变压器设计论坛里面讨论很多,不多说。还是考虑成本,尽量不在变压器里面加屏蔽层,顶多在变压器外面加个十字屏蔽。变压器一定要验算delta B值,delta B=L*Ipk/(N*Ae),L(uH),Ipk(A),N为初级砸数(T),Ae(mm2)有兴趣验证这个公式可以在最低电压输入,输出负载不断增加,看到变压器饱和波形,饱和时计算结果应该是500mT左右。变压器的VCC辅助绕组尽量用2根以上的线并绕,之前很大批量时有碰到过有几个辅助绕组轻载电压不够或者重载时VCC过压的情况,2跟以上的VCC辅助绕线能尽量耦合更好解决电压差异大这个问题。

18、更改后:变压器的设计,反激变压器设计论坛里面讨论很多,不多说。还是考虑成本,尽量不在变压器里面加屏蔽层,顶多在变压器外面加个十字屏蔽。变压器一定要验算delta B值,防止高温时磁芯饱和。delta B=L*Ipk/(N*Ae),L(uH),Ipk(A),N为初级砸数(T),Ae(mm2)。(参考TDG公司的磁芯特性(100℃)饱和磁通密度390mT,剩磁55mT,所以ΔB值一般取330mT以内,出现异常情况不饱和,一般取值小于300mT以内。我之前做反激变压器取值都是小于0.3的)附,学习zhangyiping的经验(所以一般的磁通密度选择1500高斯,变压器小的可以选大一些,变压器大的要选小一些,频彔高的减小频彔低的可以大一些吧。)

变压器的VCC辅助绕组尽量用2根以上的线并绕,之前很大批量时有碰到过有几个辅助绕组轻载电压不够或者重载时VCC过压的情况,2跟以上的VCC辅助绕线能尽量耦合更好解决电压差异大这个问题。

附注:有兴趣验证这个公式的话,可以在最低电压输入,输出负载不断增加,看到变压器饱和波形,饱和时计算结果应该是500mT左右(25℃时,饱和磁通密度510mT)。

借鉴TDG的磁芯基本特征图。

19、输出二极管效率要求高时,可以采用超低压降的肖特基二极管,成本要求高时可以用超快恢复二极管。

20、输出二极管并联的RC用于抑制电压尖峰,同时也对辐射有抑制。

21、光耦与431的配合,光耦的二极管两端可以增加一个1K-3K左右的电阻,Vout串联到光耦的电阻取值一般在100欧姆-1K之间。431上的C与RC用于调整环路稳定,动态响应等。

22、Vout的检测电阻需要有1mA左右的电流,电流太小输出误差大,电流太大,影响待机功耗。

23、输出电容选择,输出电容的纹波电流大约等于输出电流,在选择电容时纹波电流放大1.2倍以上考虑。 24、2个输出电容之间可以增加一个小电感,有助于抑制辐射干扰,有了小电感后,第一个输出电容的纹波电流就会比第二个输出电容的纹波电流大很多,所以很多电路里面第一个电容容量大,第二个电容容量较小。

25、输出Vout端可以增加一个共模电感与104电容并联,有助于传导与辐射,还能降低纹波峰峰值。

26、需要做恒流的情况可以采用专业芯片,AP4310或者TSM103等类似芯片做,用431+358都行,注意VCC的电压范围,环路调节也差不多。

27、有多路输出负载情况的话,电源的主反馈电路一定要有固定输出,或者假负载,否则会因为耦合,burst模式等问题导致其他路输出电压不稳定。28、初级次级的大地之间有接个Y电容,一般容量小于或等于222,则漏电流小于0.25mA,不同的产品认证对漏电流是有要求的,需注意。

算下来这么多,电子元器件基本能定型了,整个初略的BOM可以评审并参考报价了。BOM中元器件可以多放几个品牌方便核成本。如客户有特殊要求,可以在电路里面增加功能电路实现。如不能实现,寻找新的IC来完成,相等功率和频率下,IC的更改对外围器件影响不大。如客户温度范围的要求比较高,对应元器件的选项需要参考元器件使用温度和降额使用。

2、电源PCB设计阶段应注意的细节

1、PCB对应的SCH网络要对应,方便后续更新,花不了多少时间的。

2、PCB的元器件封装,标准库里面的按实际情况需要更改,贴片元件焊盘加大;插件元件的孔径比元件管脚大0.3mm,焊盘直径大于孔0.8mm以上,焊盘大些方便焊接,元器件过波峰焊也容易上锡,PCB厂家做出来也不容易破孔。还有很多细节的东西多了解些对生产是很大的功劳啊。

3、安规的要求在PCB上的体现,保险丝的安规输入到输出距离3mm以上,保险丝带型号需要印在PCB上。PCB的板材也有不同的安规要求,对应需要做的认证与供应商沟通能否满足要求。相应的认证编号需印到PCB上。初级到次级的距离8mm以上,Y电容注意选择Y1还是Y2的,跨距也要求8mm以上,变压器的初级与次级,用挡墙或者次级用三层绝缘线飞线等方法做爬电距离。

4、桥堆前L,N走线距离2.5mm以上,桥堆后高压+,-距离2.5mm以上。走线为大电流回路先走,面积越小越好。信号线远离大电流走线,避免干扰,IC信号检测部分的滤波电容靠近IC,信号地与功率地分开走,星形接地,或者单点接地,最后汇总到大电容的“-”引脚,避免调试时信号受干扰,或者抗扰度出状况。

5、IC方向,贴片元器件的方向,尽量放到整排整列,方便过波峰焊上锡,提高产线效率,避免阴影效应,连锡,虚焊等问题出现。

6、打AI的元器件需要根据相应的规则放置元器件,之前看过一个日本的PCB,焊盘做成水滴状,AI元件的引脚刚好在水滴状的焊盘上,漂亮。

7、PCB上的走线对辐射影响比较大,可以参考相关书籍。还有1种情况,PCB当单面板布线,弄完后,在顶层敷整块铜皮接大电容地,抑制传导和辐射很有效果。

8、布线时,还需要考虑雷击,ESD时或其他干扰的电流路径,会不会影响IC。

3、电源调试阶段应注意的细节

1、万用表先测试主电流回路上的二极管,MOSFET,有没有短路,有没有装反,变压器的感量与漏感是否都有测试,变压器同名端有没有绕错。

2、开始上电,我的习惯是先上100V的低压,PWM没有输出。用示波器看VCC,PWM脚,VCC上升到启动电压,PWM没有输出。检查各引脚的保护功能是否被触发,或者参数不对。找不到问题,查看IC的上电时序图,或者IC的datasheet里面IC启动的条件。示波器使用时需注意,3芯插头的地线要拔掉,不拔掉的话最好采用隔离探头挂波形,要不怎么炸机的都不知道。用2个以上的探头时,2根探头的COM端接同1个点,避免影响电路,或者夹错位置烧东西。

3、IC启动问题解决了,PWM有输出,发现启动时变压器啸叫。挂MOSFET的电流波形,或者看Isense脚底波形是否是三角波,有可能是饱和波形,有可能是方波。需重新核算ΔB,还有种情况,VCC绕组与主绕组绕错位置。也有输出短路的情况,还有RCD吸收部分的问题,甚至还碰到过TVS坏了短路的情况。

4、输出有了,但是输出电压不对,或者高了,或者低了。这个需要判断是初级到问题,还是次级的问题。挂输出二极管电压电流波形,是否是正常的反激波形,波形不对,估计就是同名端反了。检查光耦是否损坏,光耦正常,采用稳压管+1K电阻替换431的位置,即可判断输出反馈431部分,或者恒流,或者过载保护等保护的动作。常见问题,光耦脚位画错,导致反馈到不了前级。431封装弄错,一般431的封装有2种,脚位有镜像了的。同名端的问题会导致输出电压不对。

5、输出电压正常了,但是不是精确的12V或者24V,这个时候一般采用2个电阻并联的方式来调节到精确电压。采样电阻必须是1%或者0.5%。

6、输出能带载了,带满载变压器有响声,输出电压纹波大。挂PWM波形,是否有大小波或者开几十个周期,停几十个周期,这样的情况调节环路。431上的C与RC,现在的很多IC内部都已经集成了补偿,环路都比较好调整。环路调节没有效果,可以计算下电感感量太大或者太小,也可以重新核算Isense电阻,是否IC已经认为Isense电阻电压较小,IC工作在brust mode。可以更改Isense电阻阻值测试。

7、高低压都能带满载了,波形也正常了。测试电源效率,输入90V与264V时效率尽量做到一致(改占空比,匝比),方便后续安规测试温升。电源效率一般参考老机种效率,或者查能效等级里面的标准参考。

8、输出纹波测试,一般都有要求用47uF+104,或者10uF+104电容测试。这个电解电容的容值影响纹波电压,电容的高频低阻特性(不同品牌和系列)也会影响纹波电压。示波器测试纹波时探头上用弹簧测试探头测试可以避免干扰尖峰。输出纹波搞不定的情况下,可以改容量,改电容的系列,甚至考虑采用固态电容。

9、输出过流保护,客户要求精度高的,要在次级放电流保护电路,要求精度不高的,一般初级做过流保护,大部分IC都有集成过流或者过功率保护。过流保护一般放大1.1-1.5倍输出电流。最大输出电流时,元器件的应力都需要测试,并留有余量。电流保护如增加反馈环路可以做成恒流模式,无反馈环路一般为打嗝保护模式。做好过流保护还需要测试满载+电解电容的测试,客户端有时提出的要求并未给出是否是容性负载,能带多大的电容起机测试了后心里比较有底。

10、输出过压保护,稳定性要求高的客户会要求放2个光耦,1个正常工作的,一个是做过压保护的。无要求的,在VCC的辅助绕组处增加过压保护电路,或者IC里面已经有集成的过压保护,外围器件很少。

11、过温保护一般要看具体情况添加的,安规做高温测试时对温度都有要求,能满足安规要求温度都还可以,除非环境复杂或者异常情况,需要增加过温保护电路。

12、启动时间,一般要求为2S,或者3S内起机,都比较好做,待机功耗做到很低功率的方案,一般IC都考虑好了。没有什么问题。

13、上升时间和过冲,这个通过调节软启动和环路响应实现。

14、负载调整率和线性调整率都是通过调节环路响应来实现。

15、保持时间,更改输入大电容容量即可。

16、输出短路保护,现在IC的短路保护越做越好,一般短路时,IC的VCC辅助绕组电压低,IC靠启动电阻供电,IC启动后,Isense脚检测过流会做短路保护,停止PWM输出。一般在264V输入时短路功率最大,短路功率控制住2W以内比较安全。短路时需要测试MOSFET的电流与电压,并通过查看MOSFET的SOA图(安全工作区)对应短路是否超出设计范围。

17、空载起机后,输出电压跳。有可能是轻载时VCC的辅助绕组感应电压低导致,增加VCC绕组匝数,还有可能是输出反馈环路不稳定,需要更新环路参数。

18、带载起机或者空载切重载时电压起不来。重载时,VCC辅助绕组电压高,需查看是否过压,或者是过流保护动作。

还有变压器设计时按照正常输出带载设计,导致重载或者过流保护前变压器饱和。

19、元器件的应力都应测试,满载、过载、异常测试时元器件应力都应有余量,余量大小看公司规定和成本考虑。 性能测试与调试基本完成。调试时把自己想成是设计这颗IC的人,就能好好理解IC的工作情况并快速解决问题。 这些全都按记忆写的,有点乱,有些没有记录到,后续想到了再补上。