引言

现在,国际上基于各种算法的数字视频传输标准已有很多,但压缩编码会对视频信息带来不同程度的损失,当压缩比高(数据传输速率低)时,图像失真严重,容易出现马赛克及块效应现象。在电视台内部等要求高清晰度的场合,这种失真是不允许的。因此,本文介绍了一种全数字、无压缩多路数字视频光纤传输系统,可实现2路视频和4路音频信号的同时传输,且容易实现,传输性能好,总体性价比高。

系统设计方案

一般情况下,在非压缩视频传输系统中,通常先把视频信号经编码、复接、电光变换之后,再经光纤传输到目的地,然后经光电转换、分接、解码等处理,还原成原始的视频信号。对于单路视频传输系统,复/解复接系统一般用通用的复/解复接芯片来实现,但如果系统要传输多路视频信号,现有的复/解复接芯片是不能独立完成的。以本设计要求为例,需要满足2路视频和4路音频的同时传输。每路视频信号采用12位量化,2路视频则需要24路的数字信号,而HDMP1032芯片最多可扩展为17路数据复/解复接传输,这还不包括4路音频转换为数字信号所占用的数据位,因而仅仅通过单个复/解复接芯片不能满足要求,必须采用多次复/解复接才能完成设计。本文介绍一种基于HDMP1032/1034串行/解串行芯片,采用二次复/解复接实现多路数字视频/音频/数据在一根电缆或光纤上传输的方案,原理框图如图1所示。

图1系统设计原理框图

图2 HDMP1034A(Rx)接收端时序图

关键技术

本设计采用二次复用的方法传输2路视频信号、4路音频信号。二次复用的思想类似于脉冲编码调制。在发送端,多路模拟视频/音频信号经ADC转换为多路数字视频/音频信号,为了减轻复接单元的压力,首先将多路数字信号分别通过一个合路器进行一次复用,复用为1路或几路较高速并行数字信号,然后再将其送到复接单元G—Link进行二次复接,得到高速串行数字信号;在接收端,高速串行信号首先经过分接单元进行一次解复用,得到较高速多路并行数字信号,然后分别经分路器进行二次解复接恢复为多路数字视频/音频信号,再通过DAC转换为多路模拟信号。

整个系统的同步主时钟由一个32.768MHz的晶振提供。二次复/解复接由HDMP1032/1034串行/解串行芯片来完成,所以主要设计的是信号的一次复/解复接部分。由于4路音频信号最后合为1路串行信号进入HDMP1032/1034芯片组,所以4路音频复/解复接的时序是整个系统的关键。

视频信号的处理

首先,分别对视频和音频信号进行量化复接。两路视频经过A/D转换后,采用12位量化后输出24路数字信号,取样速率为16.384MHz,然后经过2:1的复接器。复接的具体做法是第一路A/D转换量化后的第一位A0与第二路A/D转换量化后的第一位B0复接为TX0,第一路A/D转换量化后的第二位A1与第二路A/D转换量化后的第二位B1复接为TX1,依此类推,24路视频信号复接为12路并行数据TX0、TX1、…、TX11进入HDMP1032。由于每路信号速率为16.384Mbps,故复接后信号速率为32.768Mbps。在接收端,HDMP1034仍然输出12路视频数字信号,然后通过两个反相时钟分别解出两路视频。

音频信号一次复接的实现

本设计中音频信号的采样频率为32KHz,量化精度为24位,同时进行AES3编码,转换后的单路音频码流速率为4.096Mbps。4路音频TXP0、TXP1、TXP2和TXP3经ADC转换后,通过4:1数据选择器复接成1路速率为16.384Mbps的串行数字信号TXA,这个过程是通过主时钟的4分频(F1)和8分频(F2)两个时钟的4种组合、利用时分复用的原理完成的。

作为扩展需要, TXA与一路外部扩展信号EX用16.384MHz时钟进行2:1的复接,最终得到速率为32.768Mbps的信号TXAE。这与视频信号的速率相等,保证了输入HDMP1032芯片的各数据流速率一致。在接收端,同样用音频一次复用时采用的时钟F1和F2将4路音频信号恢复出来。

高速串/并转换的实现

设计中视频/音频信号的串行传输通过HDMP1032/4A芯片组完成。HDMP1032/4A芯片组可实现高速数据链路的点对点通信,在使用中,它可以看成传送数据和控制字的“虚拟带状电缆”接口。载入Tx发射芯片的并行位可以经过一个同轴电缆或是光纤链路串行信道到达Rx接收芯片,并在Rx恢复为最初的并行格式。

在发射端,HDMP1032内部的锁相环(PLL)和时钟发生器用来产生发射芯片工作所需要的全部内部时钟。通过所需的并行码率设置控制信号TXDIV1/0的选择,PLL锁住TXCLK输入的时钟,经CIMT编码后扩展为20位(16位码位+4位编码位)。锁相完成后,芯片开始接收并行码率在TXDIV1/0设定范围内的信号。又根据控制位的状态,决定信号类型、进行编码复接、串行输出。

在接收端,高速串行数据进入Rx后,片内的时钟——数据恢复电路(CDR)从输入数据提取时钟,恢复出数据。CDR电路锁住REFCLK的频率,与抽样后的输入信号相位对齐。恢复后的数据进入解复接电路,时钟发生器根据码流速率产生内部电路所需的所有时钟。此时串行数据解复接为并行数据,再进入译码器译码,然后输出并行码。

信号经一次复接后,2路视频和4路音频复接为13路并行的数字信号,同时,为了准确恢复音频信号,保证接收端和发射端信号与复接时钟之间的相对关系不变,我们将复接时用到的时钟F1和F2也作为数据与信号并行传输,在接收端得到RF1和RF2。这样,加上2路时钟信号,总共15路数字信号进入二次复接芯片HDMP1032A的数据位。

由HDMP1032A出来的1路串行数据经光纤传输进入HDMP1034A,通过其内部处理,在接收端得到的仍然是15路数字信号,即进入HDMP1032A的并行信号。这样,音视频信号的二次复接和一次解复接已经由HDMP1032/4A芯片组完成。

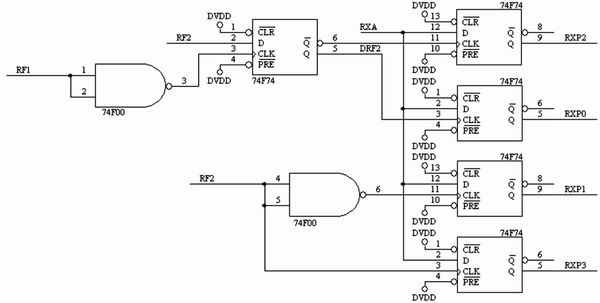

图3 音频二次解复接的电路原理图

音频二次解复接的实现

HDMP1034可自动产生两个互为反相的RXCLK0和RXCLK1,作为所有输出信号的标志信号,所有的恢复信号的相位均以这两个信号作为参考。这对于得到用于恢复各路音频的时钟信号非常重要。图2所示的是输出信号与RXCLK0和RXCLK1之间的时序关系。RX[0-15]表示HDMP1032/4A芯片组中可作为信号传输的16位并行数据位,它们与RXCLK0的下降沿存在td、典型值为2ns的延迟。事实上,作为芯片时钟输入的TXFLAG经过芯片组后得到的RXFLAG同样与各数据位相位一致。

从串行信号恢复出的各信号必须遵循的原则是用复接时用到的频率去恢复出串行流中包含的各信号。因此,首先用同样是Tx恢复出的16.384MHz的RX16MA将数据信号和外部扩展信号EX分离开,得到RXA。为了能准确地恢复RXA,所选用的16.384MHz时钟的边沿应该尽量靠近RXP[0-3]数据包的中间部分。处理的办法是将RXFLAG做为数据位,RXCLK1做为时钟,经过一个D触发器,得到16.384MHz的RX16MA,这样,RX16MA与RXAE之间存在约为5ns的延时。

对于RXP[0-3]的恢复选用的是两个4.096MHz的时钟,具体的电路如图3所示。最后用于RXP[0-3]解复接的4个时钟信号分别是DRF2及其反相信号,RF2及其经过与非门之后的信号。其中,DRF2及其反相信号分别解出RXP0和RXP2,RF2及其经过与非门之后的信号分别解出RXP3和RXP1。因为4路音频复接成的串行信号速率为16.384Mbps,因此,对相邻两路音频信号解复接的两路时钟信号应存在一个周期的延迟,对应到解复接采用的4.096MHz的时钟,即为1/4个周期的延迟。

这样,首先将4路音频与1路扩展信号分离,然后进行RXP[0-3]的解复接,最后恢复出了4路音频信号。

结语

本方案具有简单、实用、可靠性高、成本低等特点,已经成功运用于传输多路音视频及数据信息的光端机设计中。视频传输质量达到广播电视水平;音频传输质量足以满足专业级的立体声传输要求(失真<-75dB、S/N>75dB、20Hz~20kHz带内平坦度<±0.5dB)。