1引言

随着数字技术和计算机技术的不断发展,越来越多的航空电子设备采用了数字化技术,从而使数字传输成为信息传输的主要途径。ARINC429是航空电子系统中最常见的通讯总线之一,广泛用于波音(Boeing)系列、欧洲空中客车(Airbus)等机种。目前国内机载电子大多采用专用测试设备,系统通用性不高,增加了检测成本。本文介绍的ARINC429接口板设计灵活、工作可靠、有效地节约了成本,可以缓解当前ARINC429设备检测难的窘境,有广阔的应用前景。

2 系统总体设计

Altera公司在2004年发布了支持CycloneⅡFPGA系列的NIOSⅡ嵌入式微处理器。它是一款通用的RISC结构32位CPU,在软件SoPC的基础上添加NIOSⅡ软核和相应的外围接口。对设计进行综合,下载到FPGA中就可以设计一个具有特定功能的嵌入式处理器。本设计采用Altera公司的FPGA—EP2C35,引人嵌入式软核处理器NIOSⅡ作为系统的主控制器,结合ARINC429专用器件和其他外围设备实现数据的收发功能。

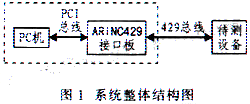

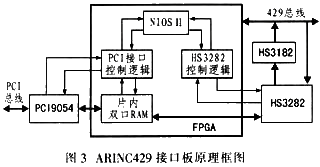

ARINC429接口板由数据收发、存储器扩展、监控、PCI总线接口等模块组成。NIOSⅡ控制协议器件HS3282完成发送数据缓存和串并转换(接收时串行转换为并行,发送时并行转换为串行),HS3182作为3282的驱动器完成差分信号转换及传输速率调节。PC机通过PCI总线与接口板通信,实现对发送、接收数据的处理和显示。NIOSⅡ自带的定时器可以设置为Watchdog。系统上电后启动运行,当主程序因外界干扰产生跑飞时对系统进行软件复位,增强了系统的抗干扰能力。系统整体结构图如图1所示。

3 硬件设计

3.1 ARINC429总线规范

ARINC429总线规范又称MARK33数字式信息传输系统(DITS:Digital Information Transfer System),它是专用于航空电子系统的航空工业标准,数据通过一对单向、差分耦合、双绞屏蔽线传输,本质属于串行通讯范畴。总线上只允许有一个发送器,但最多允许有20个接收器。数据字有25 bits和32 bits两种,以双极归零码的形式发送。数据脉冲有三种电平,即高电平,逻辑1(6.5 V~13 V);中电平(-2.5 V~2.5 V);低电平,逻辑O(-13 V~6.5 V)。中电平为发送自身时钟脉冲。字与字之间以一定间隔(4位)分开,此间隔作为字同步。ARINC429的传输速率为12.5 kb/s(低速)或者100 kb/s(高速),传输协议比较简单,属于点对点的传输协议。

3.2 HS3282与HS3182接口电路

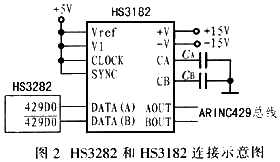

HS3282和HS3182是美国Harris公司推出的高性能CMOS总线接口电路,能够满足ARINC429总线的规范要求及类似的编码定时多路串行数据传输协议。目前,绝大多数ARINC429总线接口电路都由它们来实现。HS3282是由两个接收器和一个发送器组成,接收器和发送器分别独立工作。两个独立的接收器直接与ARINC429总线相连,当接收到一个数据字后产生相应的读请求信号,等待外部命令对数据的读取。发送器主要由先进先出(FIFO)存储器和定时电路组成,FIFO存储器可以保存8个32位数据字,定时电路按照ARINC规范的要求分隔每个Arinc字,并自动产生奇偶校验位。外部提供的工作时钟一般为1 MHz,通过软件控制可以使HS3282的接收和发送模块工作在不同的速率(100kb/s或者12.5 kb/s),从而使器件的通用性更强。需要注意的是波特率不同时,驱动器HS2182的CA、CB端的外接电容也应该不同,高速传输(100 kb/s)时,CA、CB端应该外接75 pF的电容,低速传输(12.5 kb/s)时,CA、CB端则应外接300 pF的电容。HS3282和HS3182的连接示意图如图2所示。

3.3 PCI总线接口设计

PCI总线是Intel公司推出的一种高性能局部总线,其数据总线为32位,且可扩展成64位,最大数据传输速率为128 Mb/s~256 Mb/s,远远大于ISA总线5 Mb/s的传输速度,是目前微机系统广泛使用的一种总线。PCI总线协议比较复杂,一般采用两种方式:

(1)采用可编程逻辑器件来设计控制接口。它的优点是比较灵活,用户可以根据自身的需要开发出适合于特定功能的电路,而不必实现PCI的全部功能。但是控制接口设计难度较大,开发周期长,成本高。

(2)采用专用PCI接口电路,例如AMCC公司的AMCCS5920,PLX公司的PCI9054等。通过专用电路可以实现完整的PCI主控模块和目标模块的功能。将复杂的PCI总线接口转换为相对简单的用户接口。用户只要设计转换后的总线接口即可。专用接口电路具有较低的成本和通用性,能够有效降低接口设计的难度,缩短开发时间,并能获得较好的数据传输性能。

虽然Altera公司也为NIOSⅡ处理器提供了方便使用的PCI核,但是价格昂贵。本设计中采用PLX公司的专用接口电路PCI9054,使其工作在C模式下。为了降低开发难度,采用一种较为简便的通信方式:在NIOSⅡ与PCI桥间插入双口RAM,一端地址数据线接NIOSⅡ。另一端接PCI9054。通过双口RAM转接数据.将双口RAM分为上下两个半区,PCI桥与NIOSⅡ对双口RAM交叉访问,可以大大削弱PCI的时序要求。只需少量的信号通过FPGA来实现逻辑转换.而无需总线仲裁,这种方式具有时序简单、控制信号较少、编程简单,应用方便等特点。

3.4 NIOSⅡ及外围接口电路设计

ALtera公司的QuartusⅡ软件是一个完整的多平台设计环境。具有分析、综合、布线、功耗估计等功能,能满足各种特定设计的需要,为可编程片上系统(SoPC)提供全面的设计环境。采用其中的SoPC Builder可在图形化界面内定制一个NIOSⅡ嵌入式系统.配合NIOSⅡ的软件开发工具NIOSⅡIDE,可以方便地开发从硬件到软件的完整系统,大大提高了设计效率。

硬件设计步骤如下:

1)在SoPC Builder软件中定制CPU软核。配置CPU硬件选项,如指令缓存等;增加外围设备接口,如数据存储器RAM接口、程序存储器Flash接口、JTAG调试口、HS3282接口模块等,添加外设如PCI总线接口、Watchdog等。

2)定义处理器上电复位地址。这里指定复位地址为外部Flash。系统在复位后会自动从外部Flash将用户指令读取到片内RAM中执行。

3)添加用户自定义指令,NIOSⅡ允许用户定制多达256个自定义指令。采用自定义指令可以用硬件来实现计算量较大的指令。对于频繁调用的指令可以有效地节省运算时间。本设计中将ARINC429数据的拼接和拆分用自定义指令来实现。

4)在FPGA内完成NIOSⅡ与HS3282接口模块、NIOSⅡ与PCI总线的接口模块及复位电路等。

5)系统编译完成后使用QuartusⅡ 5.0软件和ByteBlasterⅡ下载电缆通过PC机在线配置FPGA,软件设计完成后若调试通过就可以将FPGA的配置数据下载到FPGA的配置器件中。

硬件框图如图3所示。

4 软件设计

4.1 ARINC429数据的接收与发送

系统上电后应该先初始化HS3282。外部工作时钟为1MHz,内部接收和发送速率可设置为外部时钟的1/10或1/80,即100 kb/s或12.5 kb/s。设置ARINC429数据字格式为32位或者25位。采用中断的方式接收数据,HS3282有两个接收器,当有一个数据字到来后。相应的接收数据有效标志DR变为低电平,向主控制器发送读数据请求。读取接收数据时,将SEL置为0,然后给相应的EN引脚送入一定宽度的负脉冲信号,接收第一个16位字。此后把SEL置1,再给EN引脚送入一个负脉冲信号,接收第二个16位字。如果处理器忽略了该请求,则下一个接收数据会覆盖前一个数据。HS3282的数据字为16位.因此一个ARINC数据字(32位)要分两次才能读出。发送数据时要先将数据写入HS3282的内部FIFO中,向FIFO写操作过程中,当PL1由低电平跳变到高电平时.低16位数据写入FIFO的输入寄存器的低16位;当PL2由低电平跳变到高电平时.高16位数据写入FIFO输入寄存器的高16位,同时将输入寄存器的内容写入FIFO单元,连续操作8次便可将FIFO写满。第一个数据字写入后TX/R由高变低。FIFO写满后,通过启动发送使能信号ENTX.HS-3282便可将这8个数据字串行发送。当然也可以根据实际需要每次发送小于8个数据字。当FIFO为空时,TX/R由低变高,禁止发送使能信号。向FIFO重新写入数据。

4.2 NIOSⅡ软件开发

NIOSⅡ的软件开发是在HAL (hardware abstraction layer)的基础上进行的。HAL系统库是一个轻量级的运行环境.提供了与硬件通讯的简单设备驱动程序。它还集成了ANSIC标准库,这些API允许设计者用标准C函数(例如:printf,fopen,fwrite等)去存取设备。HAL类似于ARM系统中的BSP(board—support package),提供了一个一致的设备存取界面。SoPC Builder和NIOSII IDE紧密集成,在SoPC Builder生成硬件系统以后.NIOSⅡIDE能够自动生成对应的客户HAL系统库。更新硬件系统设置以后.NIOSⅡIDE能自动更新HAL的驱动设置。

软件设计步骤如下:

1)在NIOSⅡIDE中创建软件项目,NIOSⅡIDE会根据用户在SoPC Builder中的硬件配置自动生成用户HAL系统库.如系统头文件和初始化文件等。

2)利用用户HAL系统库在NIOSⅡIDE开发环境下编写程序源代码C/C++程序,编译调试代码,调试完毕后用NIOSⅡIDE提供的Flash软件Flash Programmer将生成的可执行文件烧写到Flash中。

在FPGA产品开发中嵌入NIOSⅡ软核微处理器具有高度集成的特点。本设计不仅在FPGA内集成了一个CPU,而且集成了CPU周边的硬件逻辑和外部设备接口,以及整个系统设计的逻辑译码电路。达到高度集成的目的。本系统的特点是:

1)NIOSⅡ嵌入式微处理器成本低。开发周期短,提高了产品的性价比和研发速度。

2)采用可编程逻辑器件使系统具有可升级和可扩展性,不仅可以更改FPGA的内部设计.还可以对NIOSⅡ的软件进行更新升级,灵活地满足不同的需求。