1.系统时钟概述

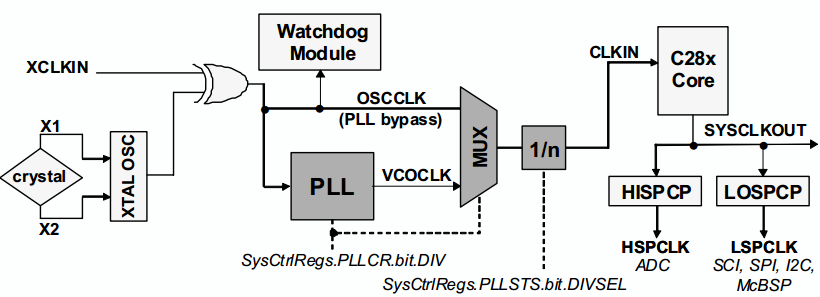

整个时钟电路的原理框图如图所示。

图1 时钟电路的原理框图

在使用有源晶振作为外部的时钟源时,DSP片内的晶体振荡电路会被旁路,外部的时钟信号有XCLKIN管脚输入DSP。看门狗定时器取OSCCLK信号作为其输入。C28x的内核会将输入的CLKIN信号转换为SYSCLKOUT信号(这就是通常我们提到的那些150MHz的信号)。SYSCLKOUT主要用来为DSP片上的一些外设提供时钟信号。按照外设的速率,一般分为需要高速时钟信号HSPCLK(顾名思义即high speed peripheral clock)的外设,如EPWM、ADC等等;以及仅需要较低的信号频率LSPCLK(顾名思义即low speed peripheral clock)的外设,主要是一些串行设备,如SCI、SPI、I2C、McBSP等。HSPCLK与LSPCLK都是通过对SYSCLKOUT进行分配得到的,主要是通过配置寄存器的控制位实现不同的分频因子。举例如下:

HSPCLK/ LSPCLK

外设时钟频率

0 0 0

SYSCLKOUT

0 0 1

SYSCLKOUT / 2

0 1 0

SYSCLKOUT / 4

0 1 1

SYSCLKOUT / 6

1 0 0

SYSCLKOUT / 8

1 0 1

SYSCLKOUT / 10

1 1 0

SYSCLKOUT / 12

1 1 1

SYSCLKOUT / 14

HSPCLK的上电默认值是SYSCLKOUT / 2,即在SYSCLKOUT为150MHz的情况下,HSPCLK默认为75MHz,所以如果想让外设工作在最高频率下一定不能忘了设置这些位。此外,如果没有正确配置的话,那外设里面的定时器,如PWM定时器的周期都将与预想的产生倍数倍的错位。LSPCLK的默认值则为SYSCLKOUT / 4。

在SysCtrlRegs.PCLKCR0、SysCtrlRegs.PCLKCR1、SysCtrlRegs.PCLKCR3寄存器中,有对各个外设时钟信号的单独的使能控制。比如,我们禁止掉SysCtrlRegs.PCLKCR0里面的ECANBENCLK,则ECANB模块没有时钟信号输入,其消耗的功率就近乎为0了。(为什么?因为CMOS电路的功耗主要是动态功耗啊!)