在数字系统的时序状态分析中,最理想的分析仪器即为逻辑分析仪(Logic

analyzer)。工程师在使用逻辑分析仪来量测系统讯号时,时常会遇到所量测到的数据不对,这就要注意有可能是选用的逻辑分析仪的负载效应造成的。以下本文将深入来探讨这个问题。

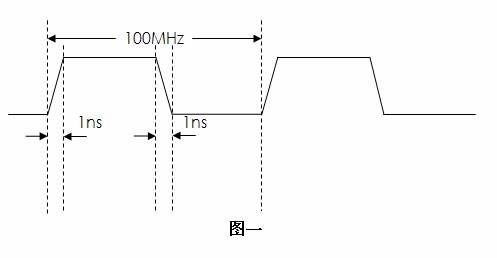

了解讯号在利用逻辑分析仪量测之前,应先了解所要测量的讯号特性,举例而言,如图一所示,假设当讯号的工作参考频率为100MHz(10ns)时,讯号的上升沿、下降沿时间为1ns左右,相当于模拟讯号的1GHz频率点;在工作参考频率为200MHz时,讯号的上升沿、下降沿时间为0.5ns左右,相当于模拟讯号的2GHz频率点。按照这种对应关系,讯号应该属于传输线的范围之内,而不能用低频讯号的分析方法来处理。

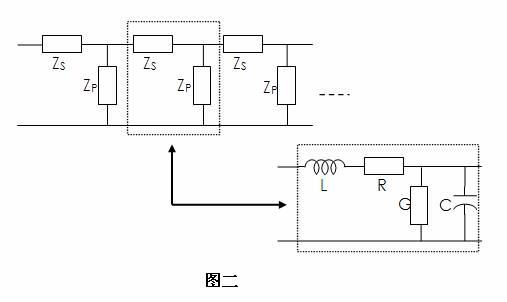

依据传输线的理论[1],高频讯号部份的走线可以建构如图二所示的模型。

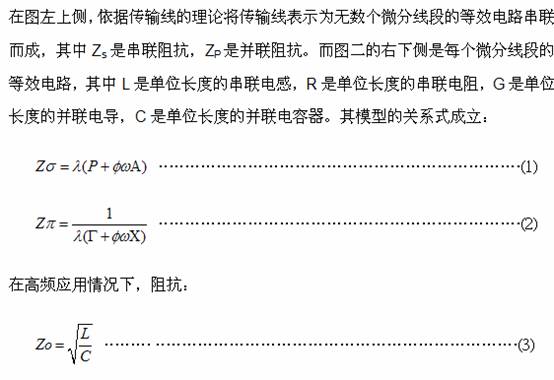

在此,若再将电路板上的其它组件也考虑进去,如连接器、缓冲器、印制板

走线的特性…等等,即会产生所谓的阻抗匹配的问题。一般情况下,连接器的

寄生电感值较大,而寄生的电容器值较小,所以特性阻抗大于印制板走线的特

性阻抗,呈现图三中所示的阻抗分布。

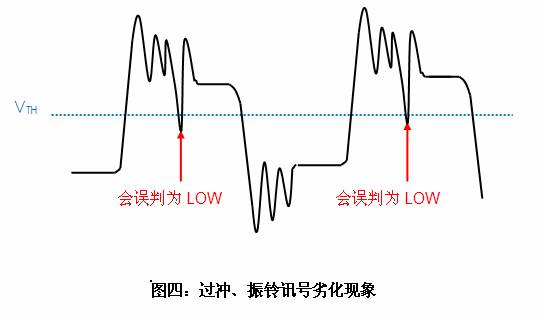

而且如果讯号的源端、末端阻抗不匹配导致阻抗特性不连续,必然会产生过冲、振

铃讯号劣化现象,如图四,易造成讯号的误判,芯片的动作将很容易出错,也必然会导致

相关的硬件系统出错,最终影响系统的稳定性。

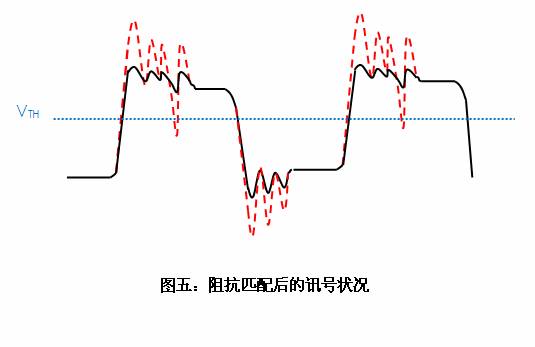

一般简单的减低过冲及振铃讯号劣化现象的作法就是做阻抗匹配来让讯号的源端、

末端阻抗特性连续,由公式(3)可容易看改变L及C值,可轻易达到增加或降低阻抗Zo。就

另外的滤通电路观点而言,任何R、L、C的改变均会有滤通的效果,而过冲及振铃相对

频率相较于讯号的频率高,故适当的R、L、C可将过冲及振铃讯号劣化现象做相当程度

的滤除或衰减。图五即为阻抗匹配后的讯号状况。

逻辑分析仪量测信道的输入阻抗

使用逻辑分析仪来量测讯号不外乎有两种状况。

(一)电路板动作正常,但需要量测芯片所传送的讯号来加以分析译码;

(二)电路板误动作,须监看芯片所传送的讯号是否有误。

不论是哪一种状况,工程师当然是需要量测出准确的讯号,最好就是电路

板上的讯号能忠实的呈现,也因如此,逻辑分析仪的量测精准性就格外来得重

要。

影响逻辑分析仪的准确性约略可由以下几个参数指标来看:

(一)量测通道的输入阻抗;

(二)内部采样率;

(三)VTH精度。

以下就单就量测通道的输入阻抗来探讨。

就如同示波器的一般,负载效应(Loading effect)也是逻辑分析仪要考虑

的重要量测因素。当我们进行量测时,常常会误以为所测得的讯号和未连入仪

器时是完全一样的。实际上每个输入探头及通道都有其输入阻抗,输入阻抗包

含了电阻、电容和电感的分量。由于在量测时,引入了额外的负载,所以就会

影响到被测电路,所以当我们分析量测时,必须考虑到探头及信道的特性及测

试电路的阻抗。

因为逻辑分析仪所要量测的讯号数量太多,故通道数量也比示波器多上好

几倍。在探头的设计上也以一段电缆排线搭配钩夹的方式处理,如此才能适用

于电路板上高密度的讯号走线量测。就探头排线搭配钩夹的阻抗特性而言,这

些探头里没有任何串联的电阻及电子组件,因此,在其工作频率范围或有用带

宽之内,探头对信号没有衰减作用,就阻抗特性而言只有电缆线与钩夹的阻

抗、容抗和感抗的分量,因此如何减低负载效应的影响?这就得完全靠逻辑分

析仪本身的阻抗特性来达成。

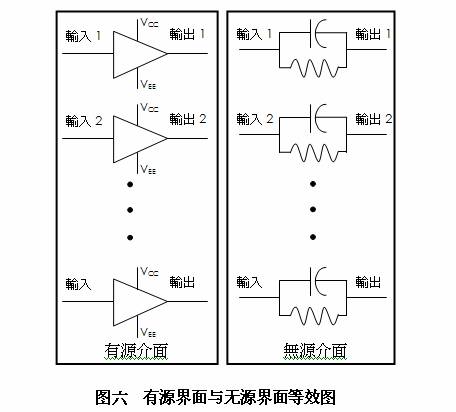

在示波器探头其中一类称为有源探头(Active Probe),探头内包含有源电子组

件可以提供放大能力;不含有源组件的探头称为无源探头(Passive Probe),其中只

包含无源组件如电阻和电容,这种探头通常对输入讯号进行衰减。而类似的,

逻辑分析仪的每个量测通道前端也有类似的做法,称之为有源接口跟无源接

口。如图六所示:下图中,无源界面不外乎亦是由电阻、电容所组成,电容将

讯号耦合到输出端,电阻是取出讯号的电压。由电组和电容的值,将可推算出

其最佳的频率响应点,不是接近此频率响应点的输入讯号将会大幅的衰减而失

真。

使用逻辑分析仪量测讯号

由上述的两个章节中,从认识讯号到量测信道的输入阻抗探讨中,更进一步的就可

以来探讨使用逻辑分析仪量测讯号。

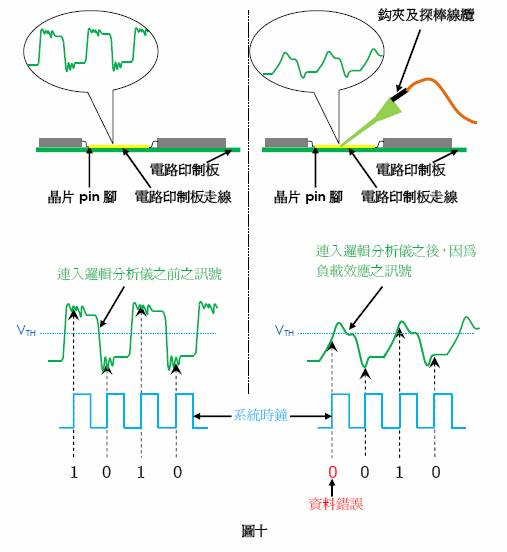

假设现有一系统,在未连入逻辑分析仪之前的动作都正常,为了要分析讯号数据,

将逻辑分析仪连上之后,系统开始出问题并当机;或者是在未连入逻辑分析仪之前的动

作不正常,为了要除错,将逻辑分析仪连上之后,系统却正常了。此时身为工程人员就

必须想到是否是逻辑分析仪的负载效应所造成结果。

图十所示是讯号受到连上逻辑分析仪之后,因为负载效应造成讯号电流额外的消耗

而振幅变小,导致接收讯号端的芯片收到错误的讯号。

图十一所示为讯号原本的过冲及振铃讯号劣化现象严重,接收讯号端的芯片收到的数据

都是错的,导致系统动作不正常,但连上逻辑分析仪之后,因为负载效应反而让过冲及

振铃讯号劣化现象减轻了,因而反倒让系统动作正常。

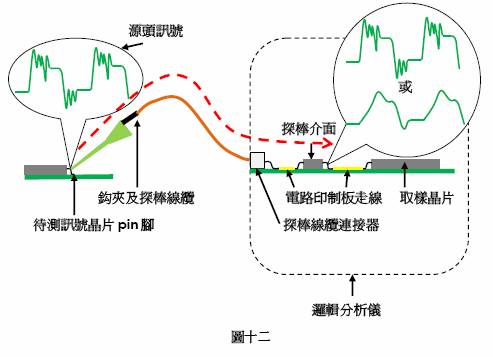

接下来,要探讨逻辑分析仪所量测到的资料是否正确的议题。假设所使用的逻辑分

析仪没有(或是只有极小的)如上文中所探讨的负载效应,不会改变系统的讯号,但是

我们却无从得知讯号透过探棒再到逻辑分析仪内部的取样芯片时,讯号是否已经有了改

变?如有改变,那是否意味着量测出来的讯号数据也有可能有误?如此这样的资料可能

便不具有分析的意义,这样的逻辑分析仪是否还是可以使用?图十二说明了可能的情况:

图十二中所示的探棒接口就是前文中所提过的有源/无源界面。这个接口如果是有

源接口,那经过这个接口输出后的讯号将比较能够呈现出源头讯号的样貌;反之,若是

无源接口,那经过这个接口输出后的讯号将会有相当程度的衰减,其衰减程度需视源头

讯号的频率与无源接口电路的频率响应关系。

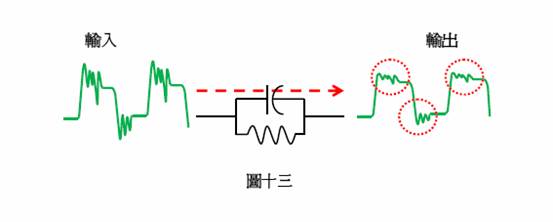

图十三所示:讯号经过无源接口电路之后,偏高频的过冲及振铃讯号已被将当程度

的衰减掉了。

逻辑分析仪实际使用状况

综观完上述的的探讨后,再来看看使用逻辑分析仪做实际的量测状况。就正常的使

用状况,工程人员不可能知道源头讯号到了逻辑分析仪内部之后会变成怎样,是会有相

当程度的失真还是会完全的呈现?除非拆了逻辑分析仪的机壳,且在清楚逻辑分析仪内

部组件及电路特性之后,才有可能量测到源头讯号到了逻辑分析仪内部之后是变成怎

样。所以在实际使用逻辑分析仪,如何辨识该逻辑分析仪是否所量测得的讯号数据是对

的还是错的?进而辨识逻辑分析仪的好坏,以下将作实际的量测实验来验证。

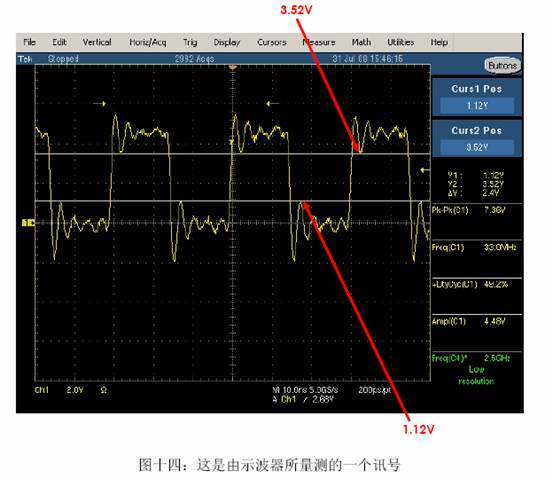

如图十四,这是由示波器所量测的一个33MHz的讯号,可看出此讯号有过冲及振铃

的现象。在图中有两个参数,好的逻辑分析仪在Threshold Voltage高于3.52V及低于

1.12V就可以测得第一次的上振铃跟下振铃。在此将使用不同的逻辑分析仪来量测此讯

号,再由逻辑分析仪所量测下来的数据来判定逻辑分析仪的优劣。

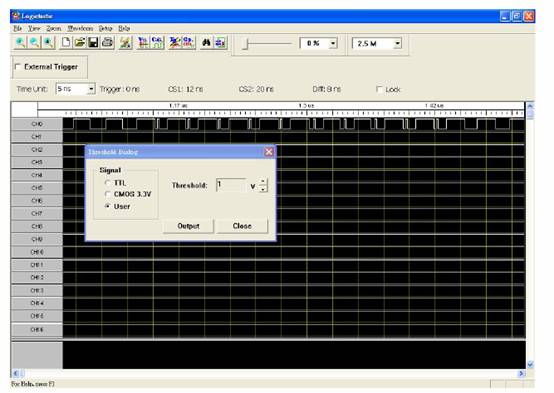

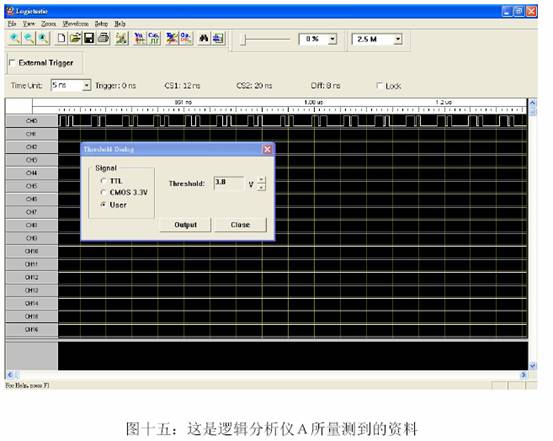

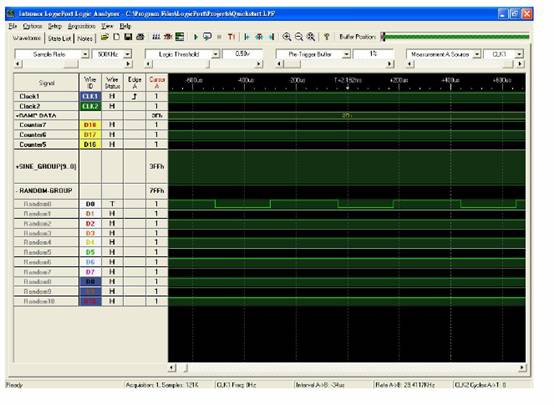

图十五与是逻辑分析仪A所量测的结果。上图是将Threshold Voltage设到1V时,就可

测到第一次的下振铃;下图是将Threshold Voltage设到3.8V时,就可测到第一次的上振

铃。

图十六是逻辑分析仪B所量测的结果。上图是将Threshold Voltage设到0.5V了,还测不

到第一次的下振铃;下图是将Threshold Voltage设到4.5V了,还测不到第一次的上振

铃。事实上,逻辑分析仪B经过繁复测试,结果是完全测不出振铃现象的。

由此可看出逻辑分析仪A是优于逻辑分析仪B的。

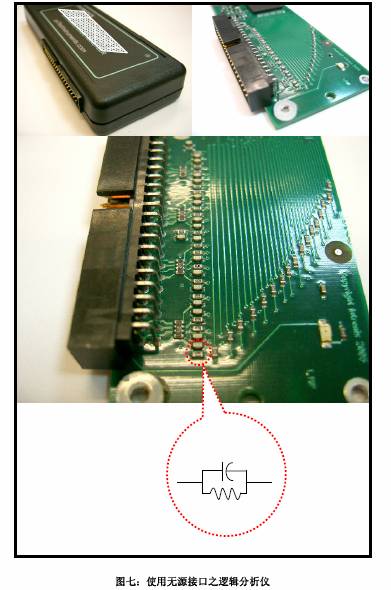

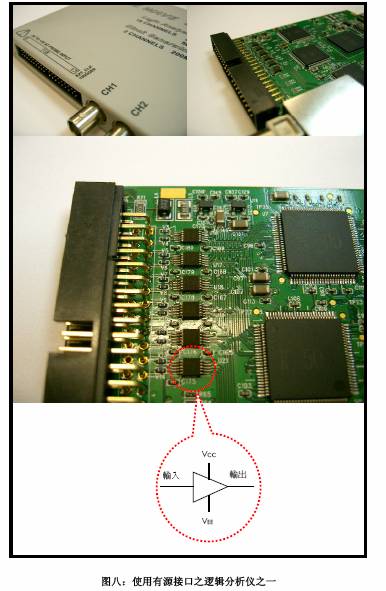

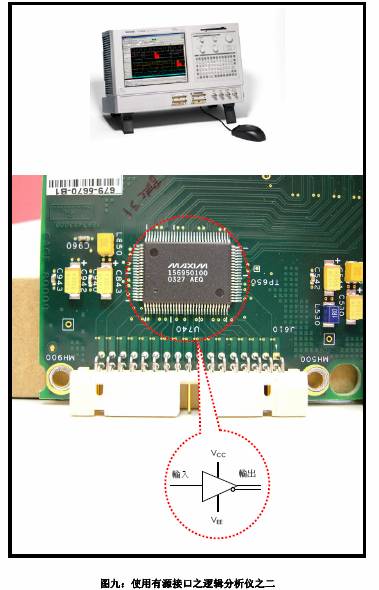

图八所示的即为逻辑分析仪A;

图七所示的即为逻辑分析仪B。

结论

逻辑分析仪不是只光看表面上软件的功能及体积的大小,如果连最基本的讯号

都无法测得或是测得的数据已经不正确了,那即使软件功能再怎样强大,外观做得

再怎样好看,所有数据结果也只能丢弃不用。

毛刺、过冲、振铃讯号是影响系统稳定性的,若仪器无法量测出来,势必会让

工程人员的Debug时间更长,甚至陷入僵局,故慎选逻辑分析仪是十分重要的。