0 引言

传统机械锁的防盗功能差,在现代高科技安防系统中无法起到作用,已逐步被更可靠、更智能的电子数字密码锁代替。目前市场上的大部分密码锁产品是以单片机为核心的,利用软件进行控制,实际应用中系统稳定性较差且成本高。本文研究的是电子密码锁的一种纯硬件实现方案,为弥补传统技术的不足,采用EDA技术在可编程芯片上实现密码的存储、运算等操作,使产品既具有硬件的安全性和高速性,又具有软件开发的灵活性和易维护性。

1 主要技术与开发环境

1.1 EDA技术及特点

EDA(Electronic Design Automation),即“电子设计自动化”,是目前电子设计领域中的主流技术。EDA技术就是依靠功能强大的电子计算机,在EDA 工具软件平台上,对以硬件描述语言为系统逻辑描述手段完成的设计文件,自动地完成逻辑编译、化简、分割、综合、优化和仿真,直至下载到可编程逻辑器件CPLD/FPGA 或专用集成电路ASIC 芯片中,实现特定的电子电路设计功能。与传统电子设计方法相比,EDA技术具有以下主要优势:

(1)可以在电子设计的各个阶段、各个层次进行计算机模拟验证;

(2)独特的自顶向下的电子设计方案;

(3)使设计者拥有完全的自主权。

1.2 硬件描述语言

VHDL(Very High Speed Integration Circuits Hard-ware Description Language),即“超高速集成电路硬件描述语言”,是当今电子设计领域的主流硬件描述语言。

它具有很好的电路行为描述能力和系统描述能力,且具有与具体硬件电路无关、与设计平台无关的特性,使得设计者可以专心致力于系统功能的实现,而不需要对不影响功能的、与工艺有关的因素花费过多的时间和精力。

1.3 开发环境

1.3.1 软件平台

QuartusⅡ是Altera公司推出的新一代开发软件,支持多种编辑输入法,包括图形输入法,基于硬件描述语言的文本编辑输入法和内存编辑输入法。它支持Al-tera 的IP 核,包含了LPM/MegaFunction 宏功能模块库,使用户可以充分利用成熟的模块,简化自己的设计、提高开发效率。

Quartus Ⅱ作为一种可编程逻辑的设计环境,其强大的设计能力已经成为广大设计人员首选的开发工具,本设计采用的是Quartus Ⅱ9.0版本作为开发平台。

1.3.2 硬件平台

CPLD(Complex Programmable Logic Device),即复杂可编程器件,由于CPLD具有编程灵活、集成度高、设计开发周期短、制造成本低、保密性强等特点,本文的硬件测试是基于MAXⅡ系列的CPLD上完成的,芯片型号为EPM240T100C5.

2 密码锁功能要求

目前市面上的电子密码锁,只允许用户输入固定位数的密码。但在实际应用中,密码位数太多,不便于老年用户记忆,而位数太少,又不能满足一些对安全性能要求高的青年用户。本文中,基于CPLD 的集成度高、成本低的特点,克服了以上缺点,让用户自行设定密码位数,该功能在同行业产品竞争中有一定的优势。

设计的电子密码锁可以完成以下功能:

(1)设置密码锁的密码位数n;

(2)n 位密码的输入及显示;

(3)密码的核对;

(4)报警功能;

(5)密码的清除和修改。

主要由密码输入电路、核心控制电路和显示输出电路构成。其中,输入电路包括矩阵式键盘、键盘扫描电路、消抖电路、译码电路等;控制电路主要完成密码的输入、核对、清除和修改等功能;输出电路控制数码显示屏上密码值的显示。

3 硬件电路设计

3.1 输入电路

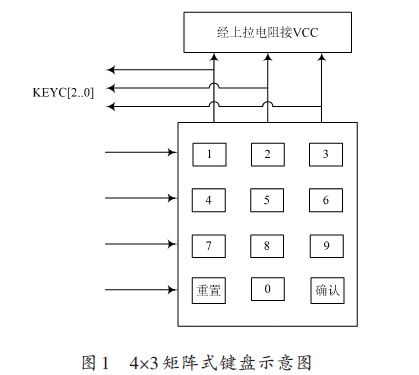

本设计采用的是4×3 矩阵式键盘,如图1所示,它是由4 根I/O线作为行线,3根I/O线作为列线,在行列线的每一个交叉点上都设置一个按键,一共有12个按键,分别代表数字0~9、确认键和设置键,如图1所示。用户如需设置密码位数,可以长按设置键达到3 s,听到提示音后再输入密码位数(本设计暂时只支持4,6,8位);如需设置新密码,可以短按设置键,提示音后再输入新的密码即可。输入电路应具备矩阵键盘扫描功能、键盘消抖功能以及译码等功能。其中,键盘扫描采用是行扫描方式,4 根I/O 线KEYR3~KEYR0 为行扫描信号,其中KEYR3对应第一行,KEYR2对应第二行,依此类推。

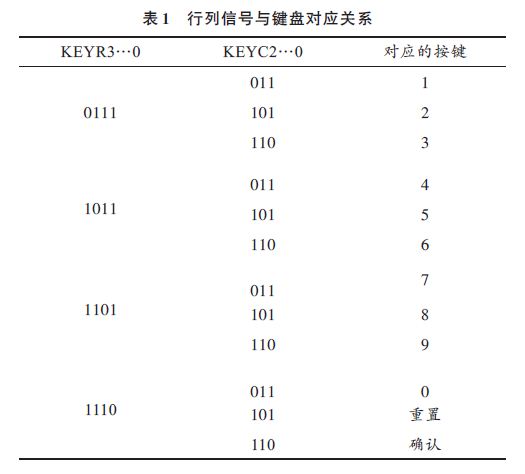

很显然,扫描信号的变化顺序为:0111,1011,1101,1110,周而复始。在扫描的过程中,当某键被按下时,从KEYC2~KEYC0 中读出的相应列信号为“0”,再将此时的4位行信号和3位列信号值送至键盘译码电路进行译码,即可得出准确的按键值。相反,若从KEYC2~KEYC0 读出的值全为“1”,则表示没有键被按下,即不做任何操作。如表1所示。

在键盘扫描过程中,扫描信号在不断变化,以判断按键的按下和抬起。快速变化的扫描信号不仅使增加了系统功耗,而且还会对其他敏感电路造成干扰[6-7].因此必须进行以下改进:将扫描模式改为键按下触发扫描方式,即当某键被按下后,才触发键盘扫描电路产生扫描时序,键被放开后,停止对键盘的扫描,使电路处于相对静止状态,以减少干扰信号。

另外,在按键按下时刻与开始扫描时刻之间加入一段较小的延时,延时结束后才允许电路开始扫描工作,可以最大限度地避免因键盘抖动带来的错误输入。

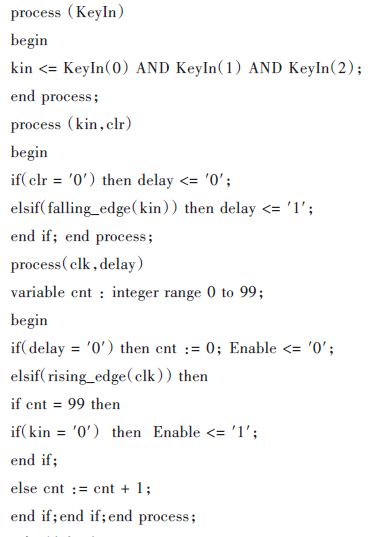

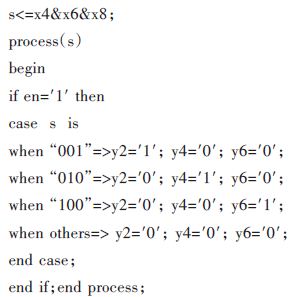

主要VHDL代码描述如下:

3.2 控制电路

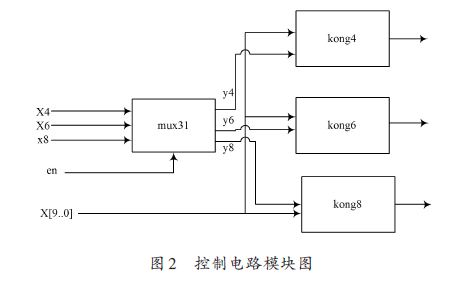

控制电路是整个系统的核心电路,能根据用户输入的密码位数进行子电路的选择。由于系统允许用户输入4 位、6 位或8 位密码,因此子电路有三个,由三选一选择器决定其中哪个电路为用户服务,见图2.

图2中,en是三选一选择器的工作使能端,它由输入电路的有效重置信号启动。当用户按下矩阵键盘上的重置按键长达3 s后,输入电路将产生en信号为‘1',从而使选择器Mux31 开始工作。如用户要设置为6 位密码,则在提示音后按下键盘上的“6”按键,其按键信号会传递给X6,由选择器决定后续控制电路为kong6.

主要VHDL代码描述如下:

对于后续控制电路kong4~kong8,都应具有密码清除、存储、核对及修改等功能。由于仅仅是操作数位数不同而已,这三个电路的VHDL语言描述过程对设计人员来说,几乎是重复操作,因此大大缩短了设计周期。

控制电路中密码的存储是利用寄存器来实现的。

寄存器是一个典型的时序逻辑电路,在某一特定时钟信号的控制下可以装载一组二进制数据并稳定存储,撤销该控制信号后信息仍然存放在寄存器中。充分利用VHDL中不完整的if语句能产生时序电路的特点,进行电路描述,而不涉及到内部触发器,开发效率高。

3.3 输出电路

输出电路要准确地将结果以十进制形式直观地显示在输出LED 上,并且当用户每输入一位密码,所有LED上的密码值左移一位。该电路属于纯组合逻辑电路,可以利用VHDL语言中的case语句描述出其电路功能。

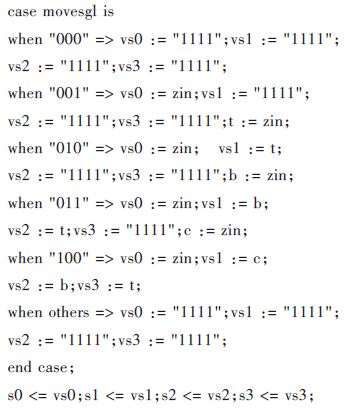

部分VHDL代码如下:

其中:movesgl 表示左移位移量;zin 是输入信号;当movesgl为“000”时表示不需要左移;当为“001”时,表示需要移动一次;“010”表示需要移动两次,以此类推。当用户通过矩阵键盘输入6 位密码时,就需要向左移动6 次,从而达到密码在LED数码管上动态左移的现象。

4 仿真与下载

4.1 仿真

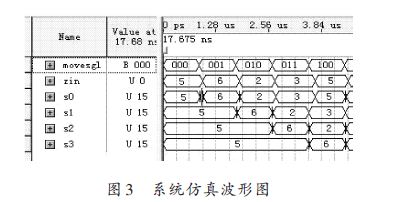

在编程下载之前,必须利用EDA 工具对设计结果进行模拟测试,即仿真。仿真是EDA 设计过程中的重要步骤。本文采用的时序仿真是最接近真实器件运行特征的仿真,仿真精度较高。以4位密码电路为例,做出了系统仿真图,如图3所示。

从图3中可以看出,通过输入端zin,先后输入了密码值“5623”,s0,s1,s2,s3存储的值在实时更新,分析波形,总结该系统基本达到了预期的功能需求,输出波形正常。

4.2 下载

在QuartusⅡ9.0软件中,利用集成EDA工具完成的下载步骤如下:

(1)根据开发板中可编程CPLD芯片EPM240T100C5的引脚特性,将本系统的顶层设计实体的端口进行引脚分配。

(2)适配器完成适配后生成了POF 格式的下载文件,再通过JTAG编程电缆向CPLD芯片进行编程。

(3)单击下载按钮Start,即对目标器件进行下载操作。当Process进度显示100%时,表示下载成功。

(4)利用开发板上的外围接口电路,进行了硬件的测试。并利用嵌入式逻辑分析仪SignalTap Ⅱ观察密码输入、修改等运行情况。

5 结语

本文弥补了传统密码锁技术上的不足,研究出了一种利用VHDL语言,结合EDA技术,在可编程芯片CPLD 上构造逻辑电路。由于所有密码的存储及运算都通过纯硬件实现,其逻辑执行速度远高于单片机。充分利用了CPLD的逻辑可编程性,开发周期短、效率高,设计出来的产品具有较高的可靠性,且功耗低、体积小、易维护,势必会在安防市场中取胜。(作者:杨斐,黄军,康浩)