pcb差分线的处理要点

a)、优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里;

b)、当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%;

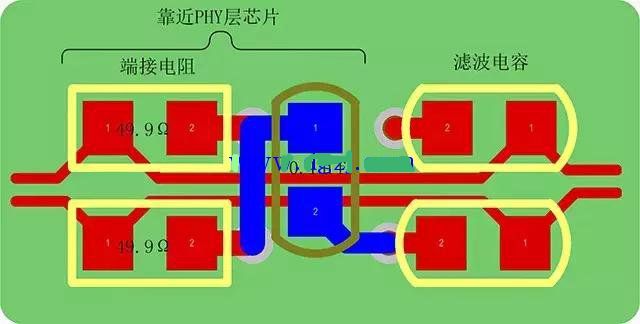

c)、差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射;

d)、差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub,这样才能对高频噪声有良好的抑制能力。

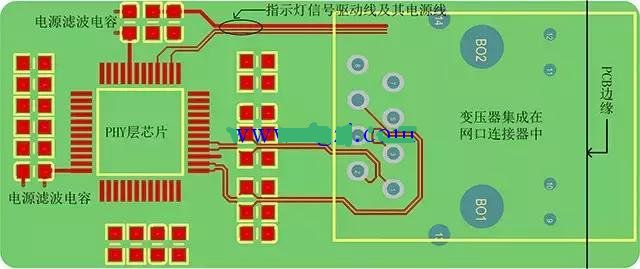

3、变压器集成在连接器的以太网电路的PCB布局、布线较不集成的相对简单很多,下图3是采用一体化连接器的网口电路的PCB布局、布线参考图:

图3 一体化连接器的网口PCB布局、布线参考图

从上图可以看出,图3和图1的不同之处在于少了网口变压器,其它大体相同。不同之处主要体现在网口变压器已集成至连接器里,所以地平面无需进行分割处理,但我们依然需要将一体化连机器的外壳连接到连续的地平面上。