在电路板上的一些高频信号会串扰到MCU电路或者MCU的I/O接口电路,形成共模电压,众所周知,共模电压在电路设计时是最让人讨厌的玩意儿,因此,设计电路板时要避免各种可能造成电路工作不正常的共模电压的串扰。

减小电路板上串扰的设计原则简单归类

1,通过合理布局使各个元器件之间的连线尽量短。

2,由于串扰程度和施加干扰信号的频率成正比,因此要使高频信号线远离敏感信号线。

3,施加干扰信号线与受到干扰信号线不仅要远离,最好要用地线隔离,并且避免相互平行走线。

4,在多层PCB板中,施加干扰信号线与受到干扰信号线或敏感信号走线要用地线隔离或相隔地层。

5,在多层PCB板中,施加干扰信号线与受到干扰信号线分别在地线或地层的相对两面,也就是隔层。

6,尽量使用输入阻抗较低的敏感电路,必要时可以使用旁路电容降低敏感电路的输入阻抗。

最后注意的是,在布线时,地线对于抑制信号串扰的作用是非常明显的,在干扰线和受干扰线直接布地线,可以将串扰降低10db左右。

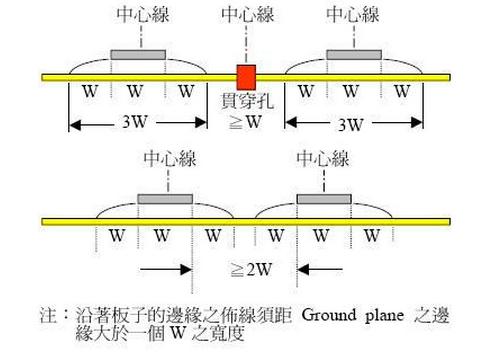

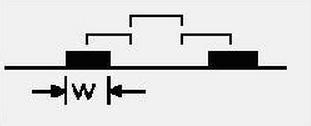

著名的3W布线规则

在抑制电路板走线信号串扰方面,有一个非常有名的3W布线规则(其中W就是布线宽度),它的内容是:对于宽度是3W的信号线,如果其他走线的中心和它的中心之间的距离大于3W,就能避免信号之间的串扰。如下图所示。

根据这个规则,3W范围内包含了信号电流产生的75%的磁通量,只要相邻的导线在这个范围之外,信号之间的串扰就不会很严重,值得注意的是,信号电流产生的磁通量的98%包含在10W范围内。